Part Number: LAUNCHXL-F280049C

Other Parts Discussed in Thread: BOOSTXL-DRV8320RS

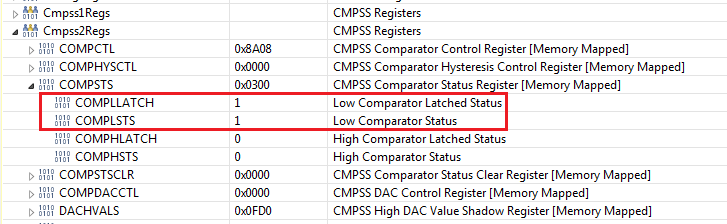

If we don't configure combinational DCA/B for Low TripINx for ePWM xBAR MUX H or L, the Low DAC digital filters remain latched after SW clears them.

If we do configure combinational DCA/B for both low/high state/path of TripINx events then SW clears Low side latches, otherwise low remain latched.

Yet the ePWM digital compare event condition is set for High state. So the low DC state should be cleared upon CPU reset and ignored but trips immediate faults upon SW reading fault now flag bits.

1. Why is it any better if not even counter productive to have both DC H/L states/path trip PWM faults even after trip sub module is configured for High trip events only?

2. Why was the CMPSSx ASYNCH DC path and the digital filter both configured in the SDK along with Output xBAR as a conflicting configuration?

3. Seemingly It is not even possible to configure an Or'd asynch latch on the ASYNCH (0) path and expect the digital filter to work (TRM Fig.16-1) but we only need CTRIPH/L unlatched events.

4. There is no ASYNCH path for the DC filter depicted (Fig.16-1) and CMPSS_OR_ASYNC_OUT_W_FILT define is oddly missing or it is it path (3)?

5. Why was CTRIPOUTH/L originally configured as they both go to the Output xBAR and are a dead end path.

Note too the DC output inversion was set on the wrong call in the SDK (corrected below). That may not have done any harm but the DC filter sample clock ticks are being ignored, seemingly odd errata passes all counts >2048 as false trips.

Patched snips:

/* Configure inverting input for internal COMPDAC(VDDA3v3) reference

* and low comparator inverted both with non-asynch filter outputs */

CMPSS_configHighComparator(obj->cmpssHandle[cnt],

CMPSS_INSRC_DAC ); // CMPSS_OR_ASYNC_OUT_W_FILT

CMPSS_configLowComparator(obj->cmpssHandle[cnt],

CMPSS_INSRC_DAC | CMPSS_INV_INVERTED);

// Configure digital filter. For this example, maximum sense values

// were used for the clock prescale, sample window size,

// Prescale: clock ticks between samples <1024, Sample window: Not >32,

// threshold: < Sample window/2 but 1< than filter threshold

CMPSS_configFilterHigh(obj->cmpssHandle[cnt], 256, 3, 2);//4,3,2

CMPSS_configFilterLow(obj->cmpssHandle[cnt], 256, 3, 2);

// Configure the output signals. CTRIPH but NOT CTRIPOUTH will be fed

// by asynchronous comparator output and only CTRIPH MUX's into ePWM xBAR

CMPSS_configOutputsHigh(obj->cmpssHandle[cnt], CMPSS_TRIP_FILTER); //CMPSS_TRIP_LATCH

//

CMPSS_configOutputsLow(obj->cmpssHandle[cnt], CMPSS_TRIP_FILTER); //CMPSS_TRIP_LATCH

// SW clear high comparator digital filter output latch

CMPSS_clearFilterLatchHigh(obj->cmpssHandle[cnt]);

// SW clear low comparator digital filter output latch

CMPSS_clearFilterLatchLow(obj->cmpssHandle[cnt]);

// Rem code below holds CMPSTSn status latched even after SW clear

// DC TRIP combinational inputs

// 18.11.12 CMPSS: EPWM_DC_COMBINATIONAL_TRIPIN2 (GPIO)

// From CCMPSSx DC A/B CTRIP-H/L

// TRM Pg.1872 Fig.18-48

/* Combinational DCA into PWM-A1 */

EPWM_enableDigitalCompareTripCombinationInput(obj->pwmHandle[cnt],

(EPWM_DC_COMBINATIONAL_TRIPIN5 |

EPWM_DC_COMBINATIONAL_TRIPIN7 | EPWM_DC_COMBINATIONAL_TRIPIN9),

EPWM_DC_TYPE_DCAH);

//EPWM_enableDigitalCompareTripCombinationInput(obj->pwmHandle[cnt],

//(EPWM_DC_COMBINATIONAL_TRIPIN5 |

//EPWM_DC_COMBINATIONAL_TRIPIN7 | EPWM_DC_COMBINATIONAL_TRIPIN9),

//EPWM_DC_TYPE_DCAL);

/* Combinational DCB into PWM-B1 */

EPWM_enableDigitalCompareTripCombinationInput(obj->pwmHandle[cnt],

(EPWM_DC_COMBINATIONAL_TRIPIN5 |

EPWM_DC_COMBINATIONAL_TRIPIN7 | EPWM_DC_COMBINATIONAL_TRIPIN9),

EPWM_DC_TYPE_DCBH);

//EPWM_enableDigitalCompareTripCombinationInput(obj->pwmHandle[cnt],

//(EPWM_DC_COMBINATIONAL_TRIPIN5 |

//EPWM_DC_COMBINATIONAL_TRIPIN7 | EPWM_DC_COMBINATIONAL_TRIPIN9),

//EPWM_DC_TYPE_DCBL);

// Trigger event when DCAH is High

EPWM_setTripZoneDigitalCompareEventCondition(obj->pwmHandle[cnt],

EPWM_TZ_DC_OUTPUT_A1,

EPWM_TZ_EVENT_DCXH_HIGH);

// Trigger event when DCAL is High

EPWM_setTripZoneDigitalCompareEventCondition(obj->pwmHandle[cnt],

EPWM_TZ_DC_OUTPUT_B1,

EPWM_TZ_EVENT_DCXL_HIGH);