Tool/software: Code Composer Studio

I tried to send message queue from CM to CPU1. The CM looks successfully send out the message queue. But the interrupt in CPU1 does not trigger. The following is the Pseudocode of both cores. Can you suggest what is missing? Thanks.

In CM main():

IPC_clearFlagLtoR(IPC_CM_L_CPU1_R, IPC_FLAG_ALL);

IPC_initMessageQueue(IPC_CM_L_CPU1_R, &messageQueue, IPC_INT0, IPC_INT0);

IPC_sync(IPC_CM_L_CPU1_R, IPC_FLAG31);

IPC_sendMessageToQueue(IPC_CM_L_CPU1_R, &messageQueue, IPC_ADDR_CORRECTION_ENABLE, &TxMsg, IPC_BLOCKING_CALL);

while(1);

In CPU1 main():

IPC_clearFlagLtoR(IPC_CPU1_L_CM_R, IPC_FLAG_ALL);

IPC_initMessageQueue(IPC_CPU1_L_CM_R, &messageQueue, IPC_INT0, IPC_INT0);

IPC_registerInterrupt(IPC_CPU1_L_CM_R, IPC_INT0, IPC_ISR1);

IPC_sync(IPC_CPU1_L_CM_R, IPC_FLAG31);

while(1);

In CPU1,

void IPC_ISR1()

{

IPC_readMessageFromQueue(IPC_CPU1_L_CM_R, &messageQueue, IPC_ADDR_CORRECTION_ENABLE, &RxMsg, IPC_NONBLOCKING_CALL);

IPC_ackFlagRtoL(IPC_CPU1_L_CM_R, IPC_FLAG0);

}

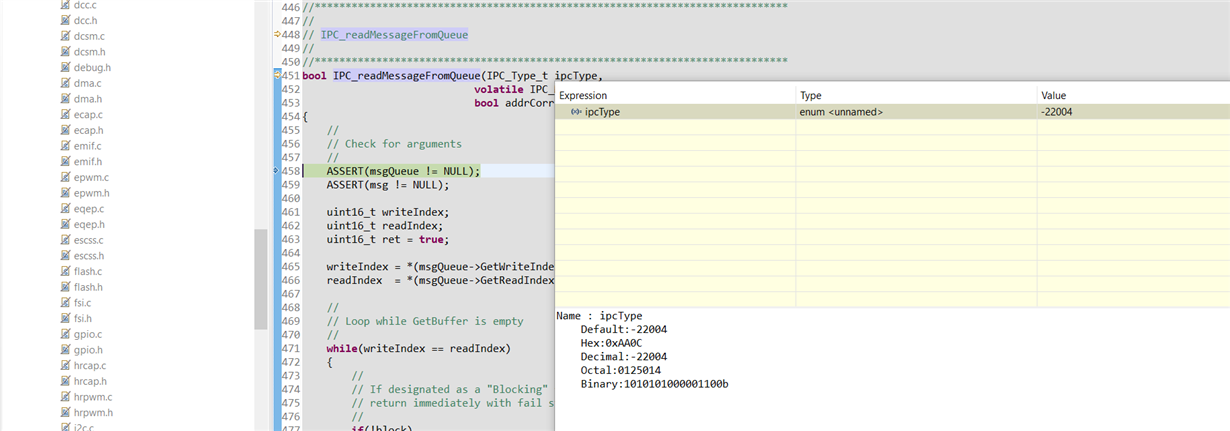

I ran both cores in debug mode. I set a break point inside IPC_ISR1() in CM. The flag PIEIFR11.INTx9 is 0 in CPU1 after it goes into an infinite while loop. After the line IPC_sendMessageToQueue() is ran in CM, I went check the PIEIFR.INTx9 and found the flag is set. However, there is no stop on the break point inside ISR. The PIEIFR11.INTx9 is the flag register for CMTOCPUxIPCINTR0 interrupt which I supposed this IFR flag is corresponded to IPC_FLAG0. Can you give any advice?

Thanks.