Other Parts Discussed in Thread: LAUNCHXL-F28379D

Hi TI C2000 Expert,

We have a trouble on TMS320F28377SPTPT :

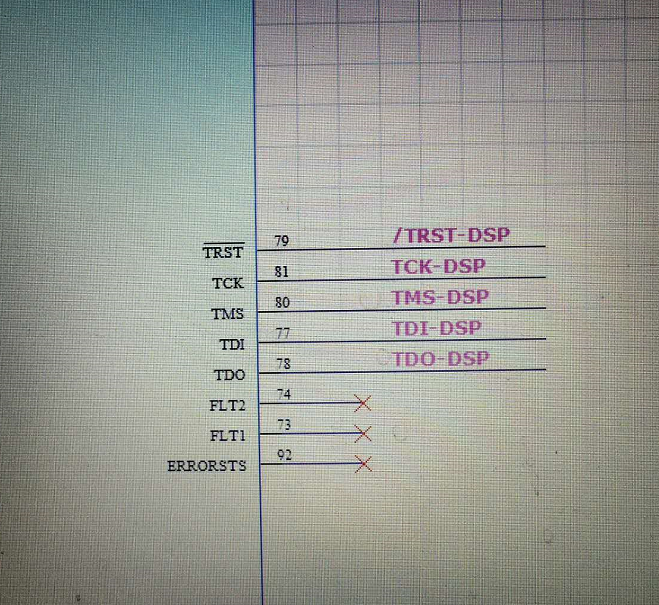

F28377 PCBA------14-pin TJAG------Emulator----usb--PC

Above is the Code burn path; Below is JTAG sche.

When we power on device with VDD3.3V, pin139(GPIO72) level status is uncertain, that will cause device enter boot mode if the level is low.

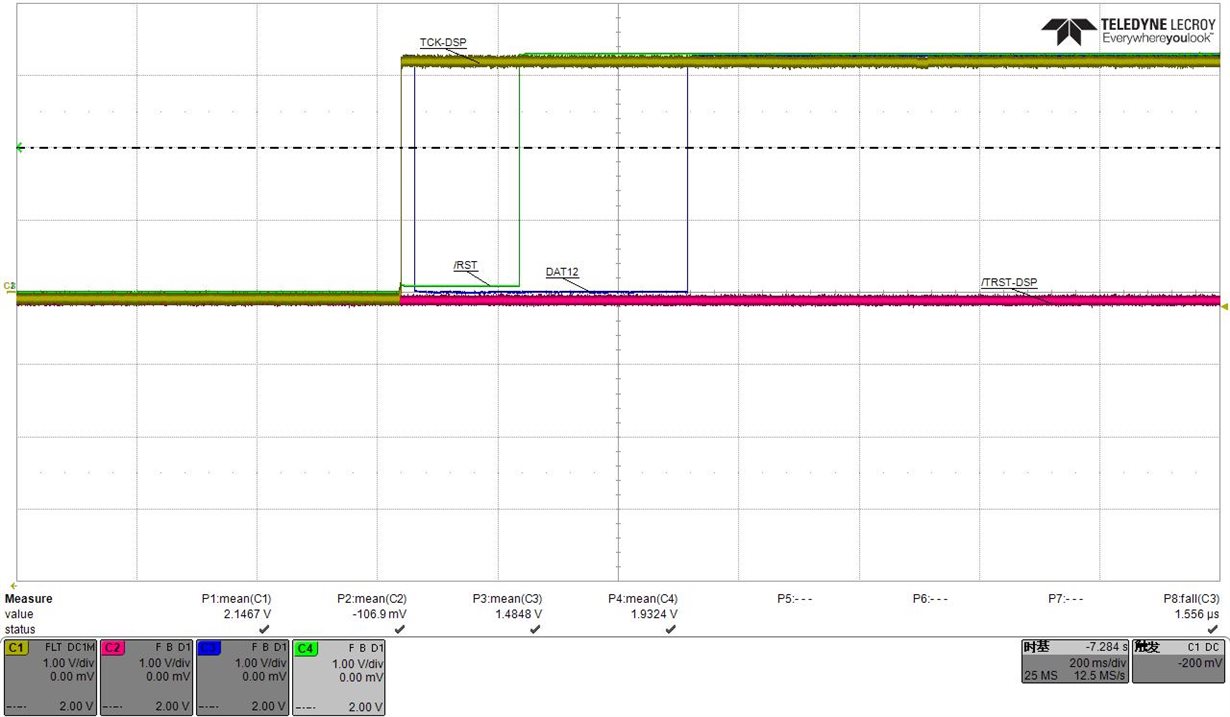

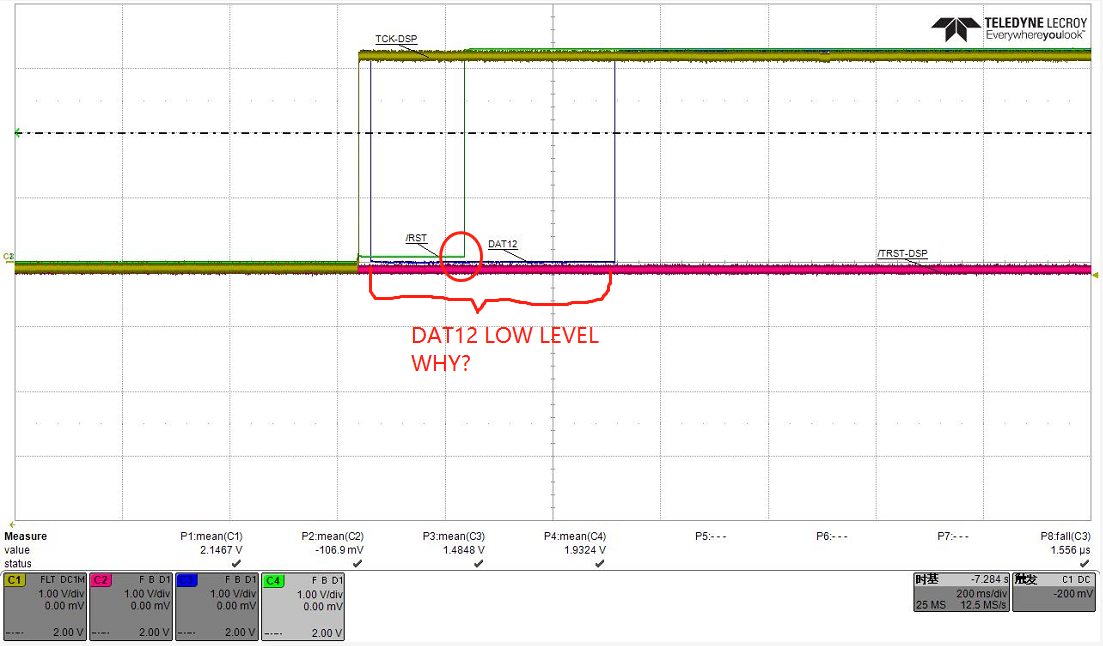

a. when the JTAG is unpluged in, then powered on VDD3.3V, We can detect the wave on pin139/GPIO72/DAT12 as below image, when /RST is trigger, the DAT12 is low, it cause device enter boot mode, that's not we want.

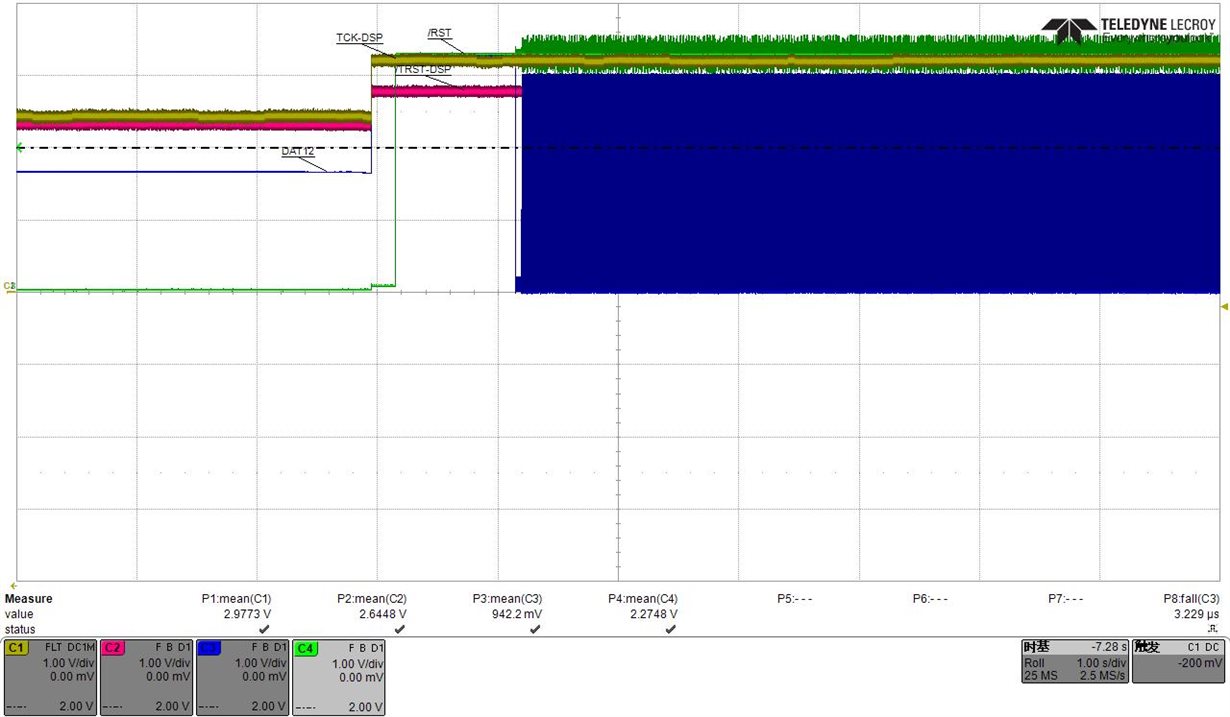

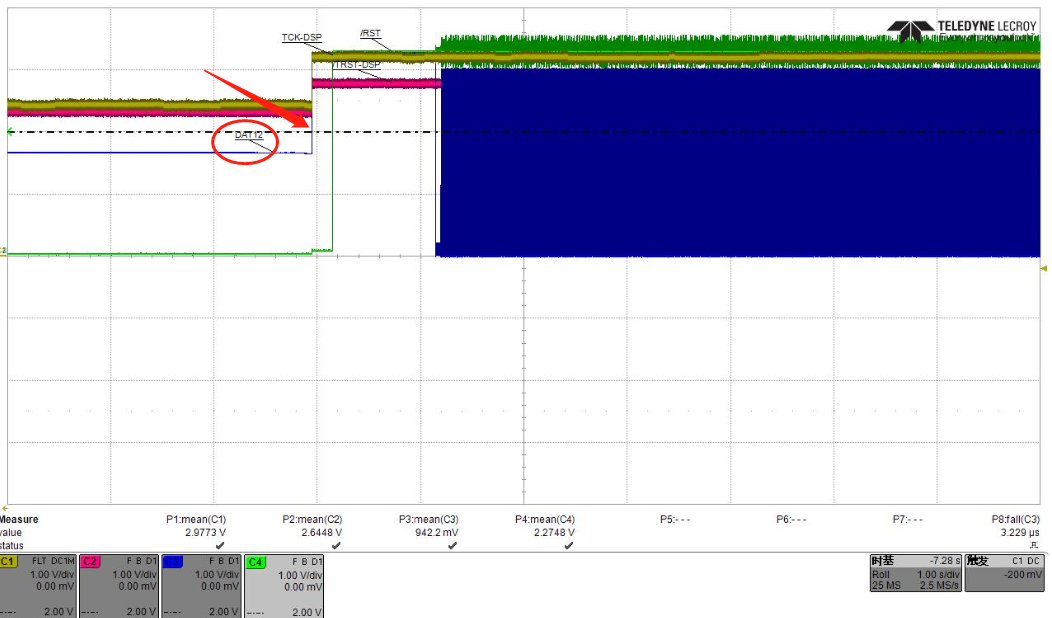

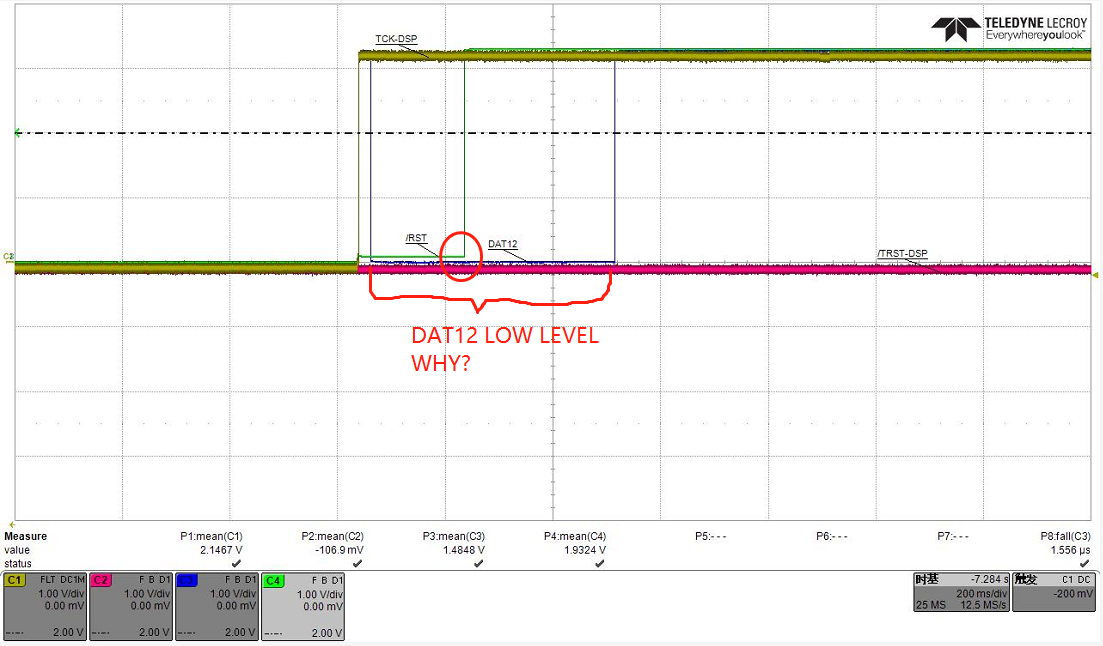

b. when the JTAG is pluged in, then powered on VDD3.3V, We can detect the wave on pin139/GPIO72/DAT12 as below image,the question is:

1. Do you know why there is an unnormal Voltage(about 1.5V)on VDD net and also on PIN139(Dat12); what is the Internal circuit architecture of this device between JTAG pin & GPIO72&VDD?

2. How to cover this issue (we don't want the device enter boot mode after device RST.)