Tool/software: Code Composer Studio

Hello all,

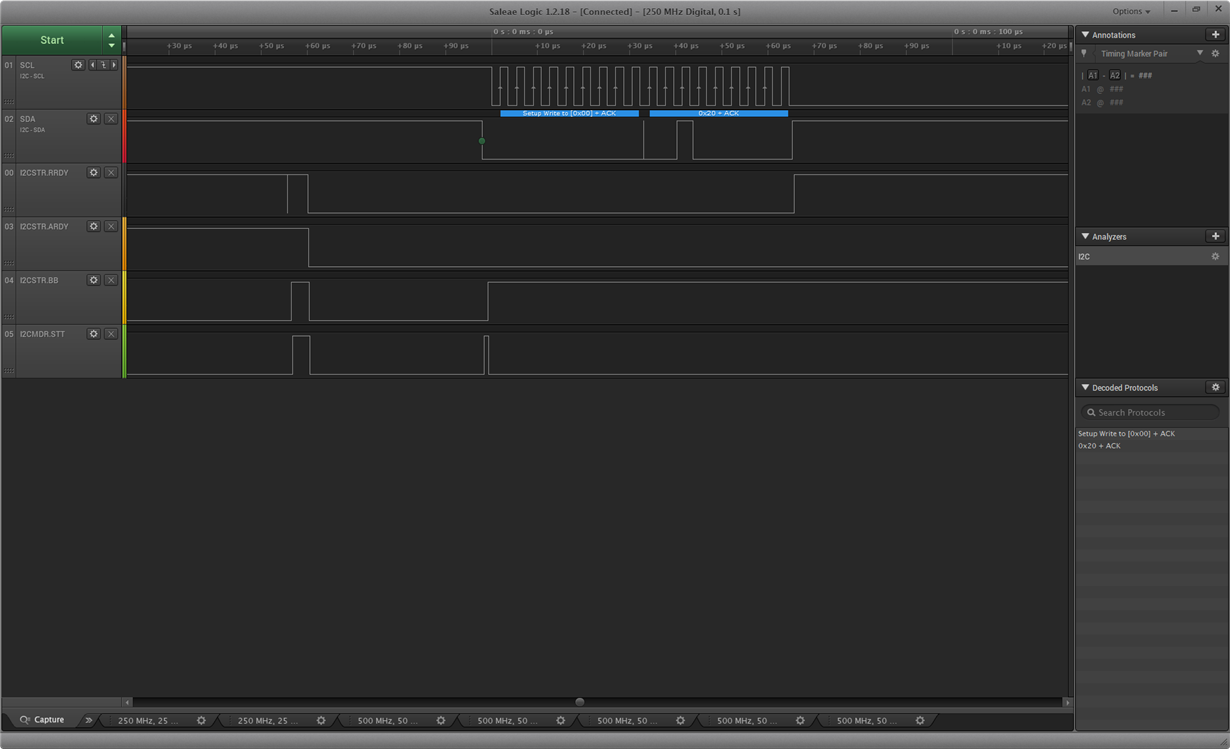

I am trying to get data from a magnetic sensor (PN:AM4096) and I'm having issues with it. The code worked well with a temperature sensor on the same bus. Essencially, I get valid data during the first time, but when I try a second time, the code hangs looking for I2caRegs.I2CMDR.bit.STT flag to clear in read_bytes function.

Uint16 AM4096class::GetAbsoluteAngle(void)

{

Uint8 data[2];

int16 result = I2C_SUCCESS;

AM4096class::SetRegisterAddress(32);

result = I2C.read_bytes((AM4096_ADDRESS_CODE | (AM4096class::Address)) , sizeof(data), data);

AM4096class::DATA_union.DATA_Registers.DATA_ADDR_33.all = data[1]<<8+data[0];

return result;

}

Uint16 I2Cclass::read_bytes(Uint16 slave_address, Uint16 count, Uint8 *out)

{

Uint16 i, ret;

GpioDataRegs.GPADAT.bit.GPIO21 = 0;

I2Cclass::start(slave_address);

GpioDataRegs.GPADAT.bit.GPIO21 = 1;

// issue repeated start

I2caRegs.I2CMDR.bit.STT = 1;

// wait for repeated start to end

I2Cclass::timeout=0;

while (I2caRegs.I2CMDR.bit.STT != 0)

{

I2Cclass::I2Cclass::timeout++;

if(I2Cclass::I2Cclass::timeout>TIMEOUT_LIMIT)

{

return I2C_ERROR;

}

}

// non-repeat mode

I2caRegs.I2CMDR.bit.RM = 0;

// set data count

I2caRegs.I2CCNT = count;

// generate STOP condition when the data counter counts down to 0

I2caRegs.I2CMDR.bit.STP = 1;

// receiver mode

I2caRegs.I2CMDR.bit.TRX = 0;

for (i = 0; i < count; ++i)

{

// wait until the data receive register is ready to be read

I2Cclass::timeout=0;

while (I2caRegs.I2CSTR.bit.RRDY != 1)

{

I2Cclass::timeout++;

if(I2Cclass::timeout>TIMEOUT_LIMIT)

return I2C_ERROR;

}

out[i] = I2caRegs.I2CDRR;

}

return I2C_SUCCESS;

}

Uint16 I2Cclass::start(Uint16 slave_address)

{

// load slave address

I2caRegs.I2CSAR = slave_address;

// wait for STOP condition

I2Cclass::timeout=0;

while (I2caRegs.I2CMDR.bit.STP != 0)

{

I2Cclass::timeout++;

if(I2Cclass::timeout>TIMEOUT_LIMIT)

return I2C_ERROR;

}

// master mode

I2caRegs.I2CMDR.bit.MST = 1;

// generate START condition

I2caRegs.I2CMDR.bit.STT = 1;

return I2C_SUCCESS;

}

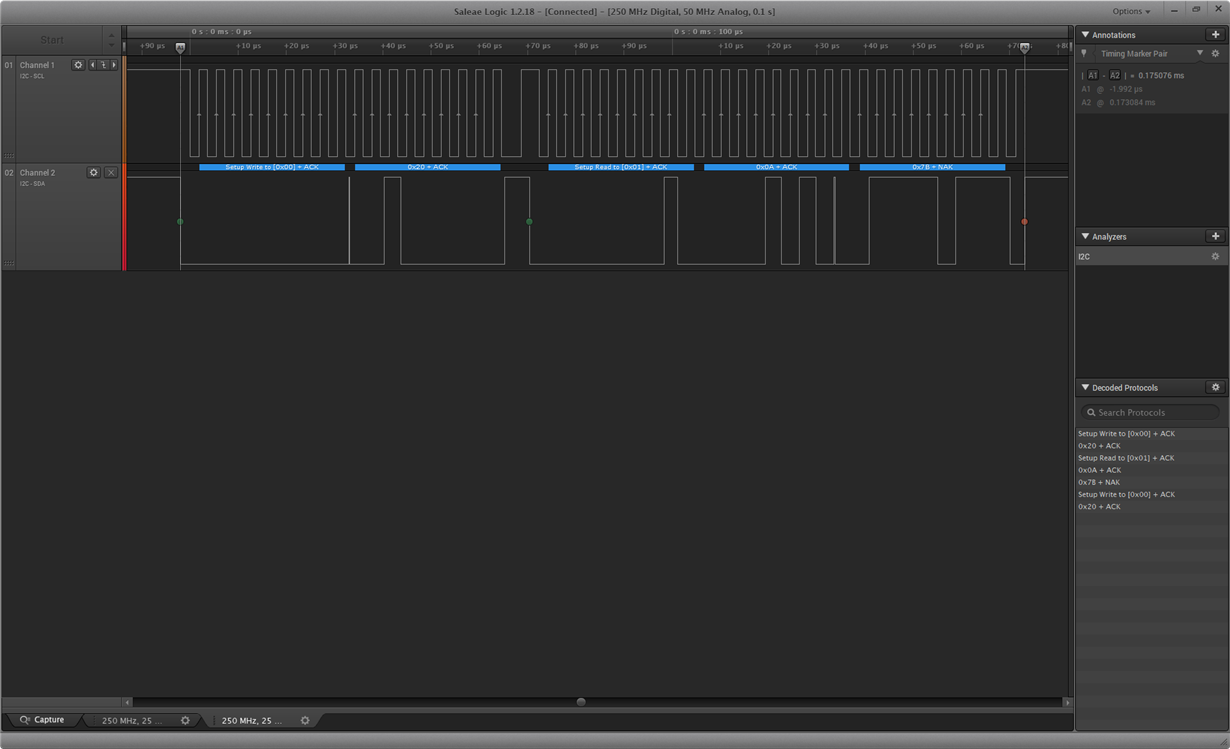

This picture below is the first request. It returns the correct value.

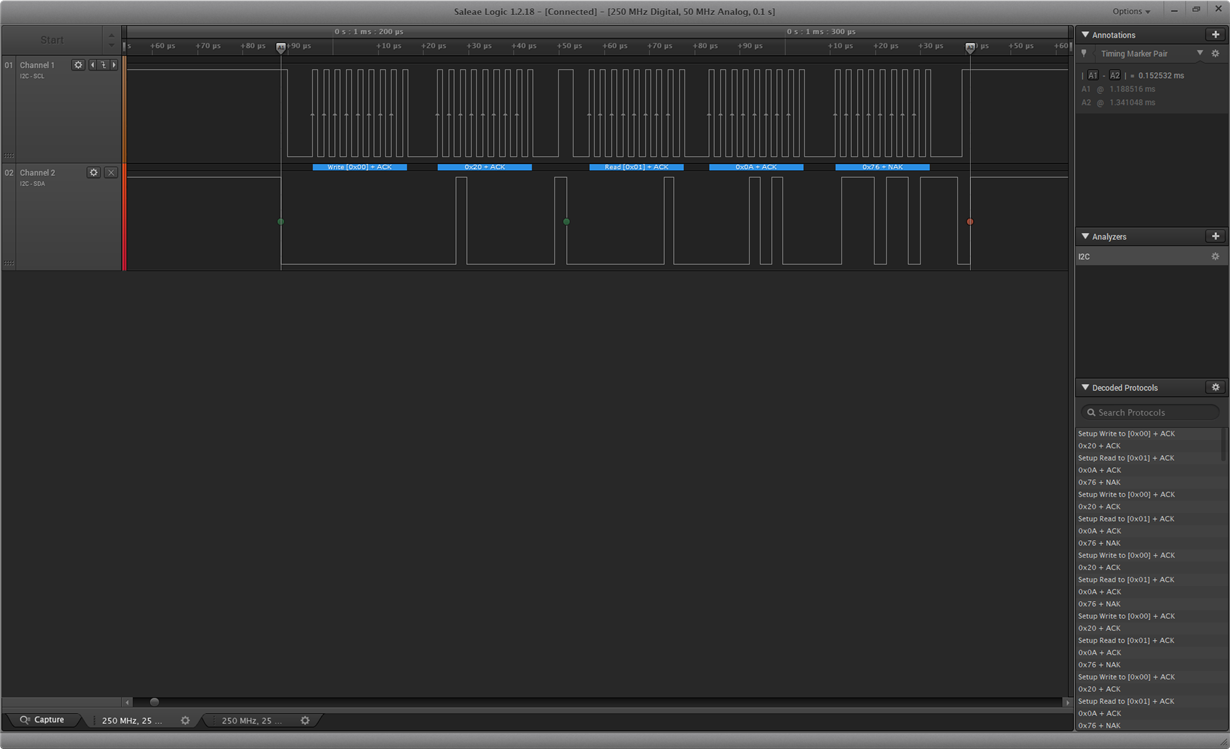

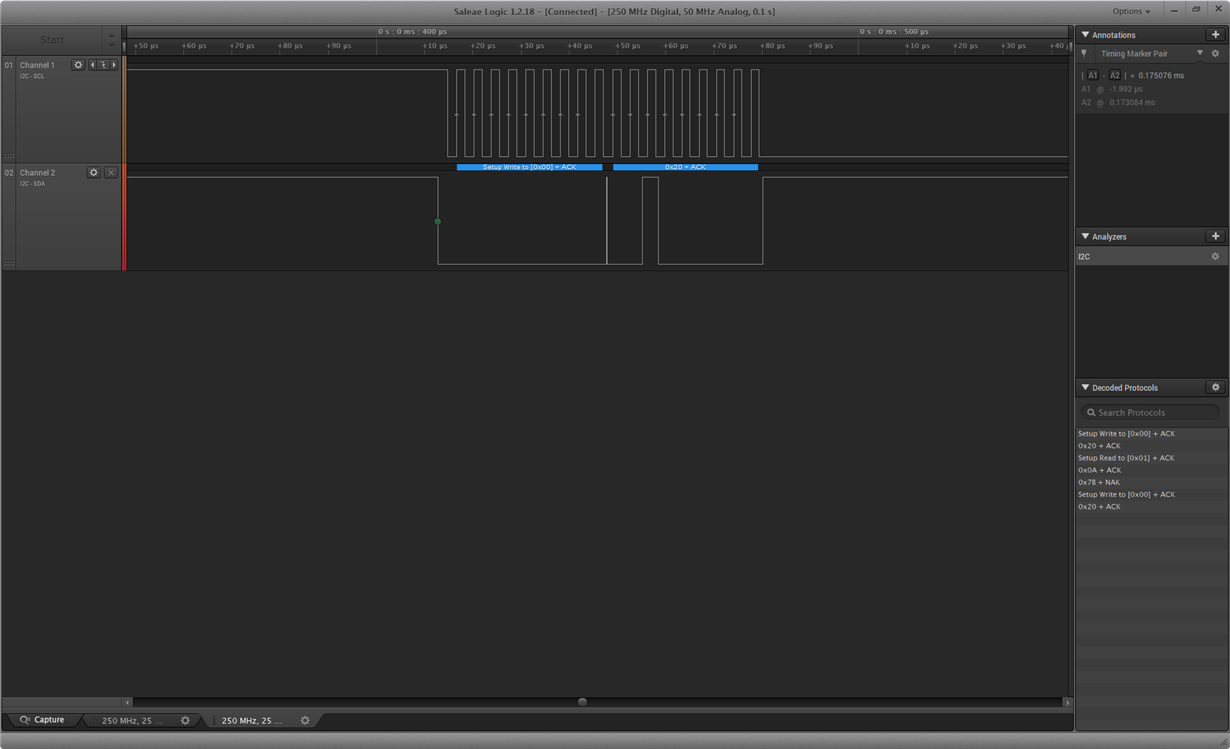

This second image shows the I2C bus hanging. It's able to send the slave and register address.

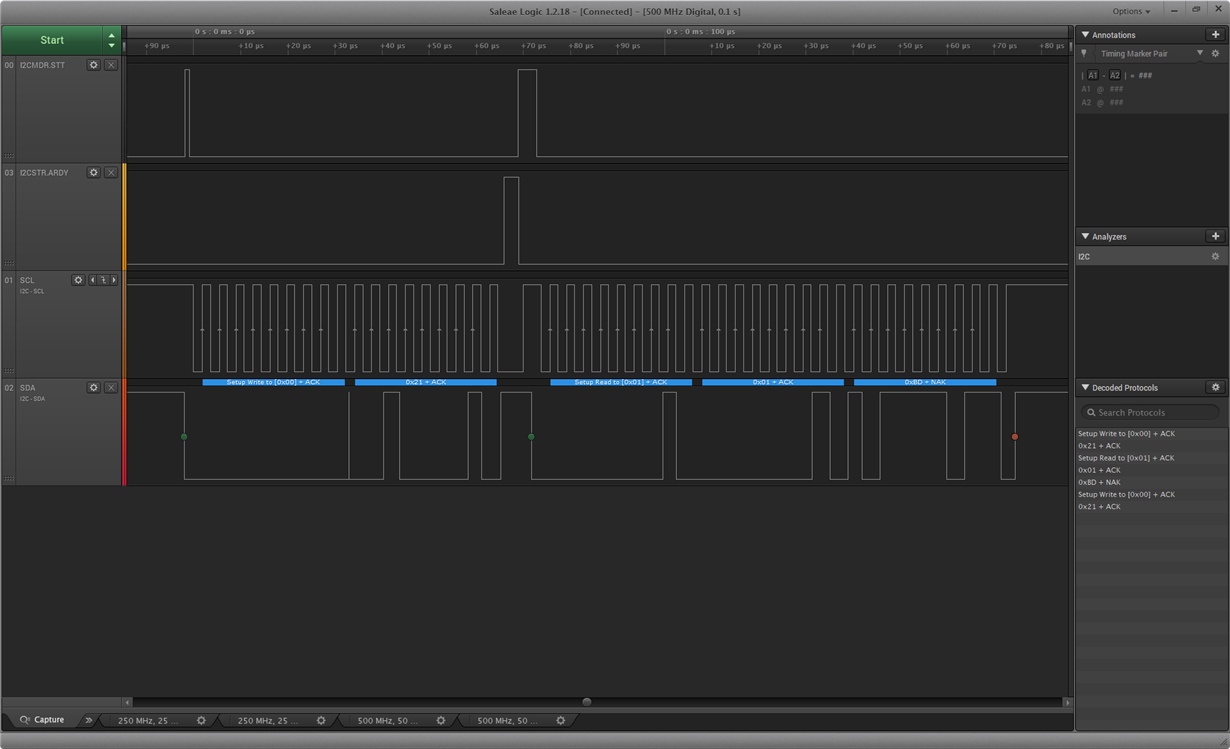

This image is when running the sensor from an arduino. It works every time.

Could someone please shine some light on this? Thank you!