Hi expert,

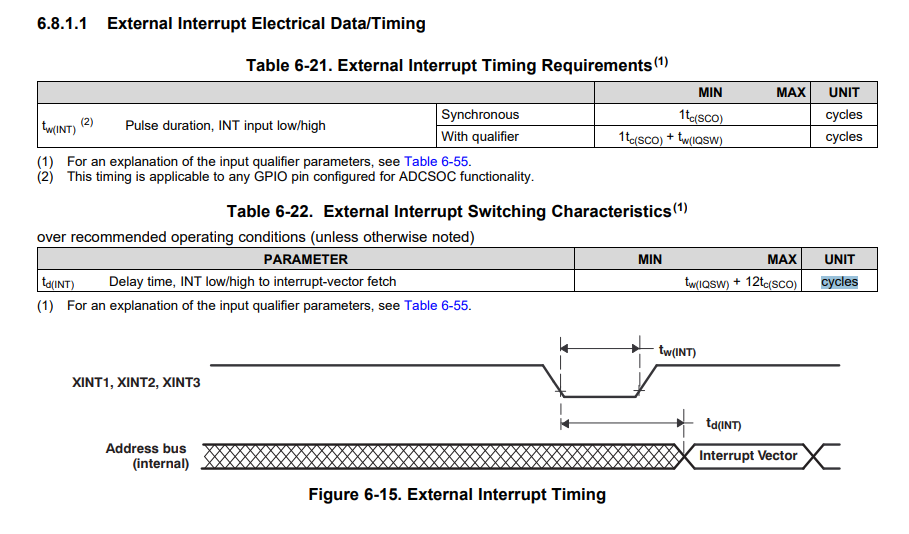

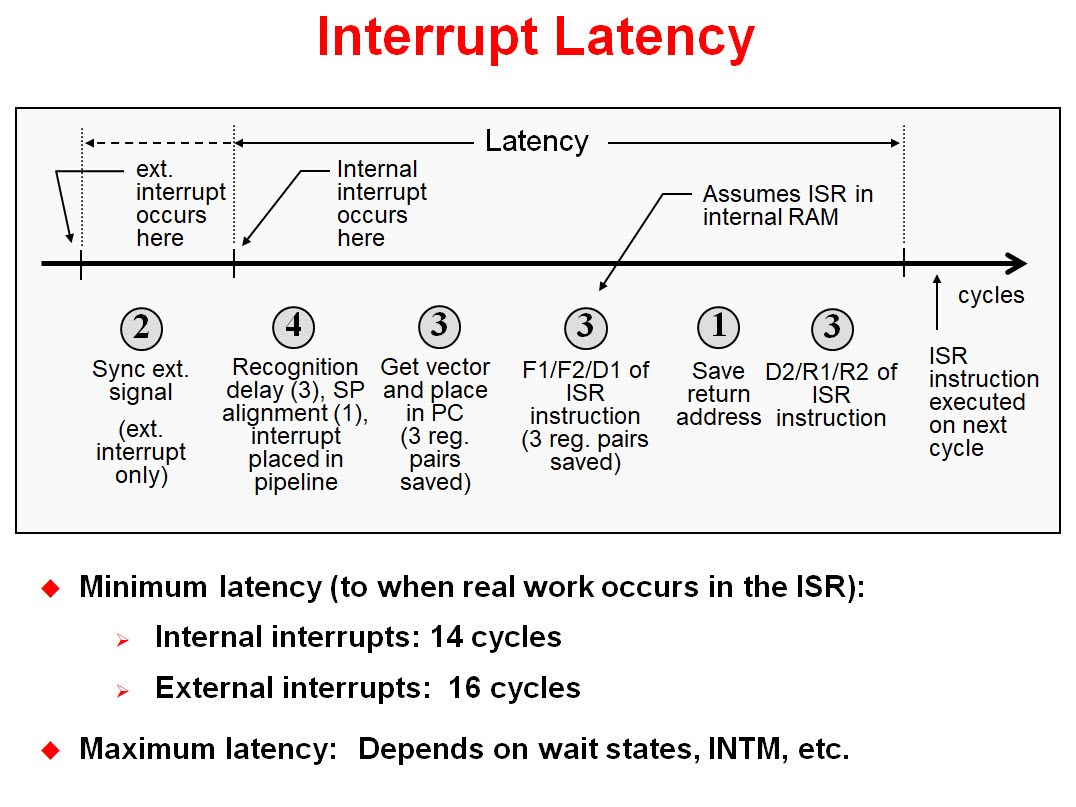

my customer wants to use comparator output to GPIO or capture to achieve edge interrupt on F28027.

However, they found the latency is too large, about 700ns.

so, my questions are:

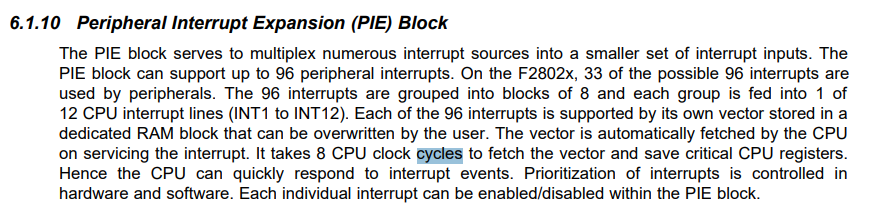

1. where can i get the interrupt latency, the time from GPIO input toggle and CPU service the interrupt.

(I think it should be several CPU clycles, however I can not find it now.)

2.if there is another method to achieve edge interrupt for comparator module?

BR

Emma