Part Number: TMS320F28075

Hi team,

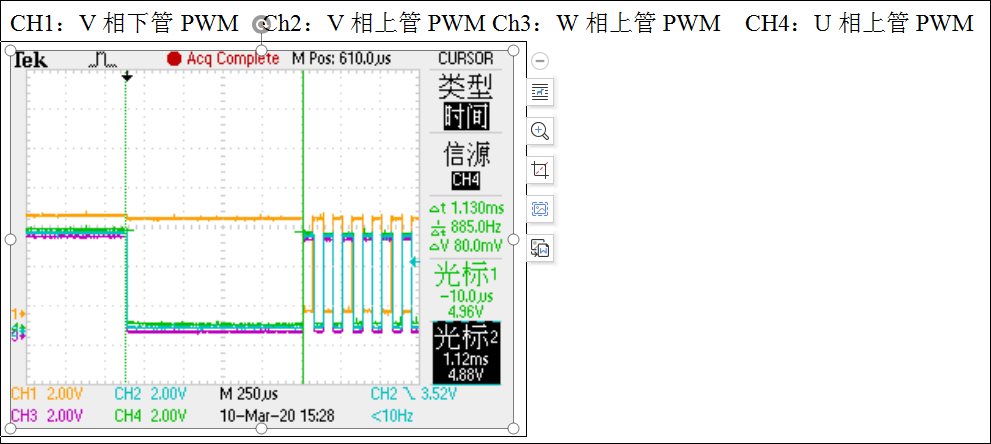

I am supporting my customer testing their system protection function. Basically, they are testing to pull high with a OST trip and then recover the normal after clearing the OST flag.

However, there is a 10% opportunity that all the PWM channel would output a preiod of LOW state instead of normal PWM waveform.

The PWM intialization is as attached text file while the PWM disable/enable function is as the following picture.

Obviously this all low output would threat customer's system safety(customer is using an inverted input gate driver). Comments are welcomed.

Regards,

Brian