Tool/software: Code Composer Studio

Dear

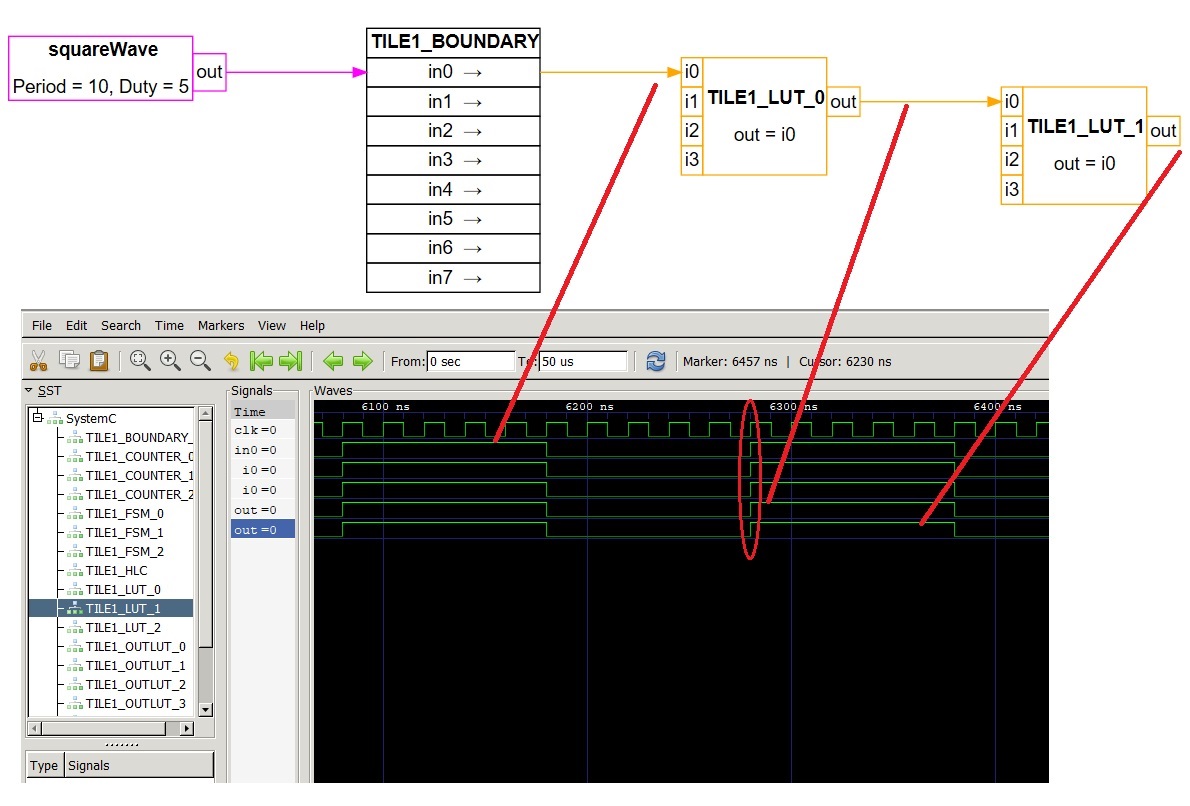

I want to detect the rising and falling edge on a GPIO in CLB.

the input of BOUNDARY can support easily,

but the question is the BOUNDARY is only for simulation.

how can I detect the both edges in reality?

thanks!

BR

jjl3