Part Number: TMS320F28388D

Other Parts Discussed in Thread: TMDXCNCD28388D, C2000WARE

Hello,

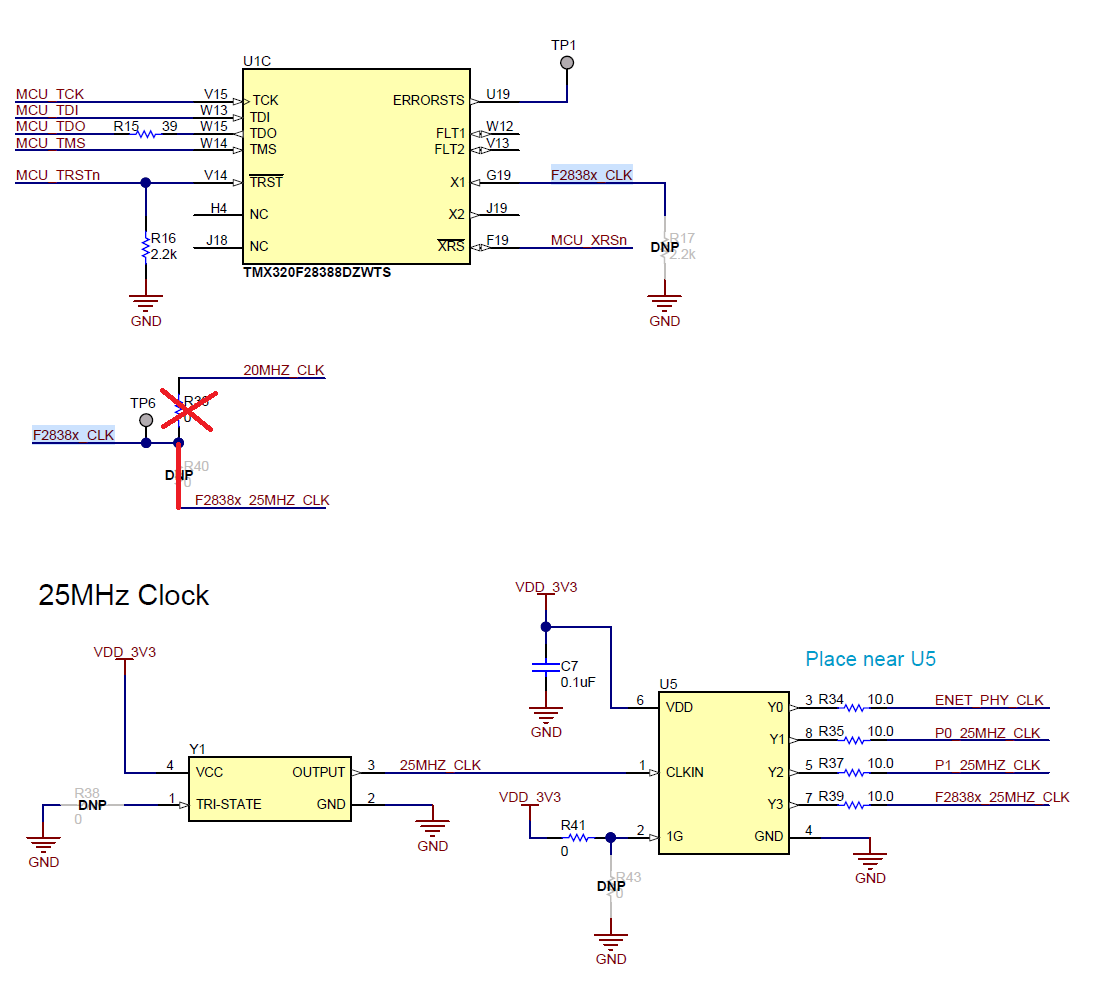

I am using TI Eval board (TMDXCNCD28388D) with F28388D processor. The input clock is configured as 25MHz (0-ohm resistor selector changed from default 20MHz (R36 removed, R40 added). Requested SysCLK frequency is 200MHz. I found that using different PLL settings (REFDIV,ODIV,IMULT) I get clock frequency close to requested 200MHz but frequency error strongly depends on PLL setting. Error vary from 0.6% to 3.4%.

For verification I have used two independent methods:

1. Toggle GPIO (1 toggle per n-th PWM periods) to measure frequency using osciloscope.

2. Using DCC - code is from C2000Ware examples (compare input to output clock frequency ratio.)

Each time I get correlated results from both methods - in this way I claim error not come from verification error and does not depends on input clock.

Moreover, the best results I get so far was with severe specification violation (INTCLK=5MHz or lower).

Example settings I have applied:

1.

REFDIV=0x04;

IMULT=0x50;

ODIV = 0x00;

SYSCLK_DIV = 0x01;

which results in error ~0.8%

2.

REFDIV=0x01;

IMULT=0x10;

ODIV = 0x00;

SYSCLK_DIV = 0x00;

which results in error ~1.5%

Questions:

1. Where this error come from?

2. Why frequency error depends on PLL settings?

3. Are there any known issues with clock/PLL circuitry on Evaluation Board?

Best Regards,

Milosz Przybylowicz