Other Parts Discussed in Thread: C2000WARE

Hi,

I am using TI Safe-TI STA for doing set of Diagnostic Tests on my custom TMS320F28377S PCB. This query is particularly regarding one test, STA_MARCH_COPY

- Running without any fault injected - This test works without any issue. The Process i see is,

- Note that am running this test on GS0 (0x00C000, ramfuncs) for 64 32bit words only for initial testing. - I tired it on the ebss RAM also, result is same as below...

- Start By Copying content from Test Address (for the length) to Copy Address

- Apply the March Test with the PATTERN Selected

- Copy back the content from Copy Address to Test Address.

- Check Memory Error using STL_March_checkErrorStatus() and call PASS/FAIL

- This test results in a PASS. Content restored back to the address.

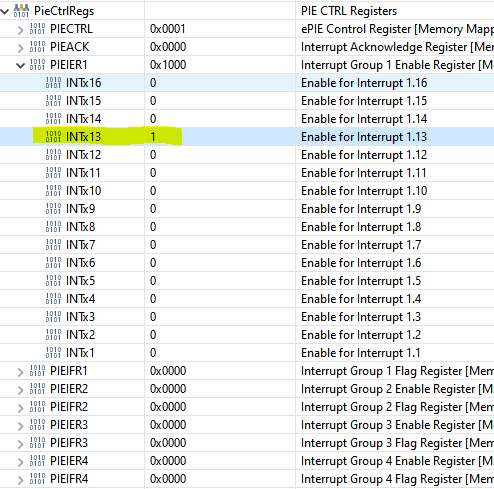

- Running the test with fault injected.

- Here the test is run on the same memory as above.

- Error injected using an xorMask - 0x00000001. I can see one bit flipping in the first word after this satement.

- Following this the code starts the March Function (which is an asm file)

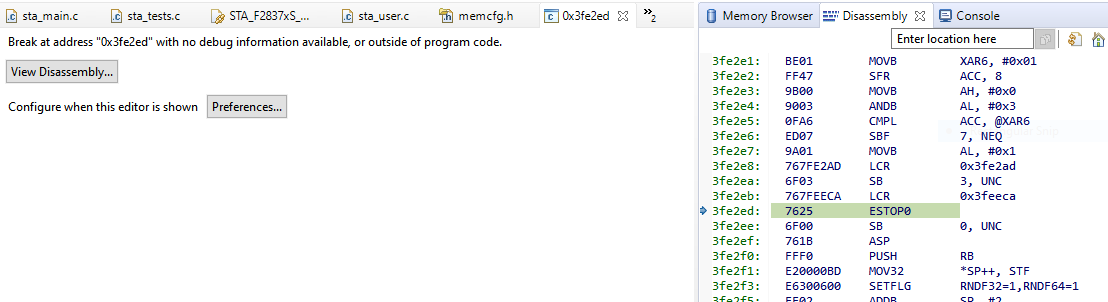

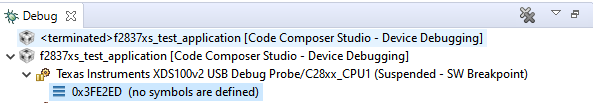

- I stepped through the asm file and code go no further than aAscend section... the code ends up in undefined memory and stops. I am not sure why !

Any reason why code fails at the point indicated in Point 2.d. Am stuck with this for several days now. Any help would be great. I cant share the whole project here, but i can definitely share the diagnostics test code sections if need be. Please help me out on this. This is tied to a Regulatory UL1998 test which is coming up in few weeks. I need grip on this before that.