Hii,

I am using the C2000 TMS320F28004x series DSP and facing an issue in ADC sensing. I am sensing analog input on all A, B, and C ADCs. Some details about peripheral configurations:

- I am using 3.3V internal reference for all 3 ADCs.

- 3.3 V supply to the analog section of MCU is constant and connected Capacitors as per the datasheet.

- I have put a 2.2uF capacitor(as per datasheet) between VrefH and VrefL pin of each of ADCs which is constant(No glitch).

- My PWM generates a signal to start the conversion for each of ADC's channels. After the end of conversion, one ADC interrupt is triggered, where I read ADC converted counts. Interrupt doesn't overflow. (uses 65% time for calculation)

- I converted analog input into digital by ADC. further, I convert this digital value into analog by DAC to probe on DSO.

On ADC A I am sensing 5 channels and it works fine. On ADC B I am sensing 3 channels and 1 channel is giving glitches. on ADC C 1 out of 5 channels is giving glitches. Glitches happen on PIN B2 and C1 pins. I tried by changing SOC configurations but it didn't improve.

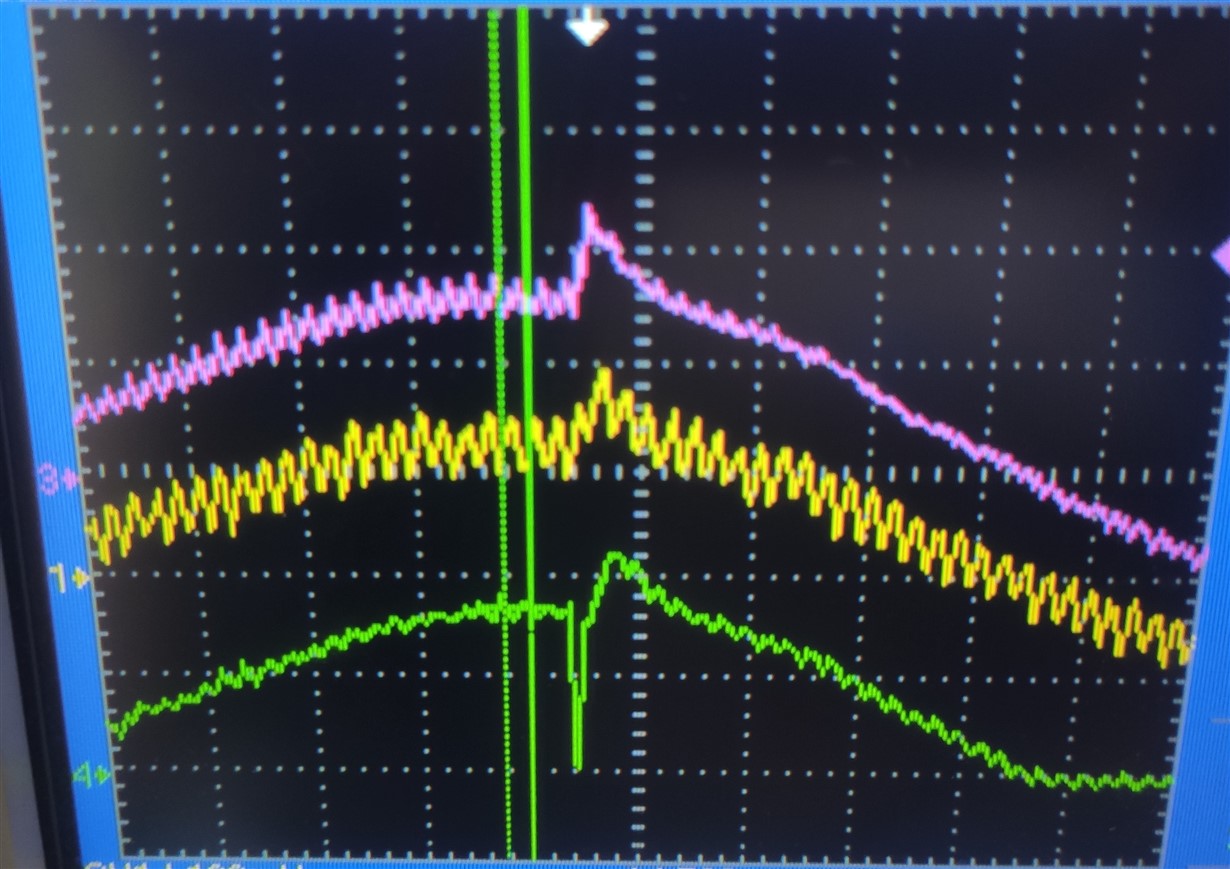

I probed analog voltage on B2 and C1 pins(input), but it is not having any fluctuations. So the input to ADC pin is not having glitch but converted Digital Result(observed on DSO by DAC module) is having a glitch. I am attaching the waveforms image below.

Yellow is the ADC pin input voltage. I am converting that ADC count into analog again by the DAC module. Note that, glitch stays for only one sampling time. (one-time conversion module is giving wrong digital counts)

Edit:

I am adding code for ADC configuration:

void InitADC()

{

//Set Voltage reference for ADCA, ADCB and ADCC

SetVREF(ADC_ADCA, ADC_INTERNAL, ADC_VREF3P3); //VREF 3.3

SetVREF(ADC_ADCC, ADC_INTERNAL, ADC_VREF3P3); //VREF 3.3

SetVREF(ADC_ADCB, ADC_INTERNAL, ADC_VREF3P3); //VREF 3.3

EALLOW;

AdcaRegs.ADCCTL2.bit.PRESCALE = 6; //Prescaler is 4 //systemclock is 100Mhz,ADC clock is 25Mhz

AdcaRegs.ADCCTL1.bit.INTPULSEPOS = 1; //Interrupt after Conversion

AdcaRegs.ADCCTL1.bit.ADCPWDNZ = 1; //Powerup ADC

AdccRegs.ADCCTL2.bit.PRESCALE = 6; //Prescaler is 4

AdccRegs.ADCCTL1.bit.INTPULSEPOS = 1; //Interrupt after Conversion

AdccRegs.ADCCTL1.bit.ADCPWDNZ = 1; //Powerup ADC

AdcbRegs.ADCCTL2.bit.PRESCALE = 6; //Prescaler is 4

AdcbRegs.ADCCTL1.bit.INTPULSEPOS = 1; //Interrupt after Conversion

AdcbRegs.ADCCTL1.bit.ADCPWDNZ = 1; //Powerup ADC

EDIS;

DELAY_US(1000); //1 ms delay to setup supply

//EOC5 of ADCA is Generating Interrupt by INT1SEL

EALLOW;

AdcaRegs.ADCSOC0CTL.bit.CHSEL = 0; // SOC0 will convert pin A1

AdcaRegs.ADCSOC0CTL.bit.ACQPS = 30; // Sample window is 30 SYSCLK cycles

AdcaRegs.ADCSOC0CTL.bit.TRIGSEL = 5; // Trigger on ePWM1 SOCA

AdcaRegs.ADCSOC1CTL.bit.CHSEL = 1;

AdcaRegs.ADCSOC1CTL.bit.ACQPS = 30;

AdcaRegs.ADCSOC1CTL.bit.TRIGSEL = 5;

AdcaRegs.ADCSOC2CTL.bit.CHSEL = 2;

AdcaRegs.ADCSOC2CTL.bit.ACQPS = 30;

AdcaRegs.ADCSOC2CTL.bit.TRIGSEL = 5;

AdcaRegs.ADCSOC4CTL.bit.CHSEL = 4;

AdcaRegs.ADCSOC4CTL.bit.ACQPS = 30;

AdcaRegs.ADCSOC4CTL.bit.TRIGSEL = 5;

AdcaRegs.ADCSOC5CTL.bit.CHSEL = 5;

AdcaRegs.ADCSOC5CTL.bit.ACQPS = 30;

AdcaRegs.ADCSOC5CTL.bit.TRIGSEL = 5;

AdcaRegs.ADCINTSEL1N2.bit.INT1SEL = 5; // End of SOC5 will set INT1 flag

AdcaRegs.ADCINTSEL1N2.bit.INT1E = 1; // Enable INT1 flag

AdcaRegs.ADCINTFLGCLR.bit.ADCINT1 = 1; // INT1 flag is cleared

AdcbRegs.ADCSOC1CTL.bit.CHSEL = 1;

AdcbRegs.ADCSOC1CTL.bit.ACQPS = 30;

AdcbRegs.ADCSOC1CTL.bit.TRIGSEL = 5;

AdcbRegs.ADCSOC2CTL.bit.CHSEL = 2;

AdcbRegs.ADCSOC2CTL.bit.ACQPS = 30;

AdcbRegs.ADCSOC2CTL.bit.TRIGSEL = 5;

AdcbRegs.ADCSOC3CTL.bit.CHSEL = 3;

AdcbRegs.ADCSOC3CTL.bit.ACQPS = 30;

AdcbRegs.ADCSOC3CTL.bit.TRIGSEL = 5;

AdccRegs.ADCSOC0CTL.bit.CHSEL = 0;

AdccRegs.ADCSOC0CTL.bit.ACQPS = 30;

AdccRegs.ADCSOC0CTL.bit.TRIGSEL = 5;

AdccRegs.ADCSOC1CTL.bit.CHSEL = 1;

AdccRegs.ADCSOC1CTL.bit.ACQPS = 30;

AdccRegs.ADCSOC1CTL.bit.TRIGSEL = 5;

AdccRegs.ADCSOC2CTL.bit.CHSEL = 3;

AdccRegs.ADCSOC2CTL.bit.ACQPS = 30;

AdccRegs.ADCSOC2CTL.bit.TRIGSEL = 5;

AdccRegs.ADCSOC3CTL.bit.CHSEL = 5;

AdccRegs.ADCSOC3CTL.bit.ACQPS = 30;

AdccRegs.ADCSOC3CTL.bit.TRIGSEL = 5;

AdccRegs.ADCSOC4CTL.bit.CHSEL = 14;

AdccRegs.ADCSOC4CTL.bit.ACQPS = 30;

AdccRegs.ADCSOC4CTL.bit.TRIGSEL = 5;

EDIS;

}//InitADC