hi,

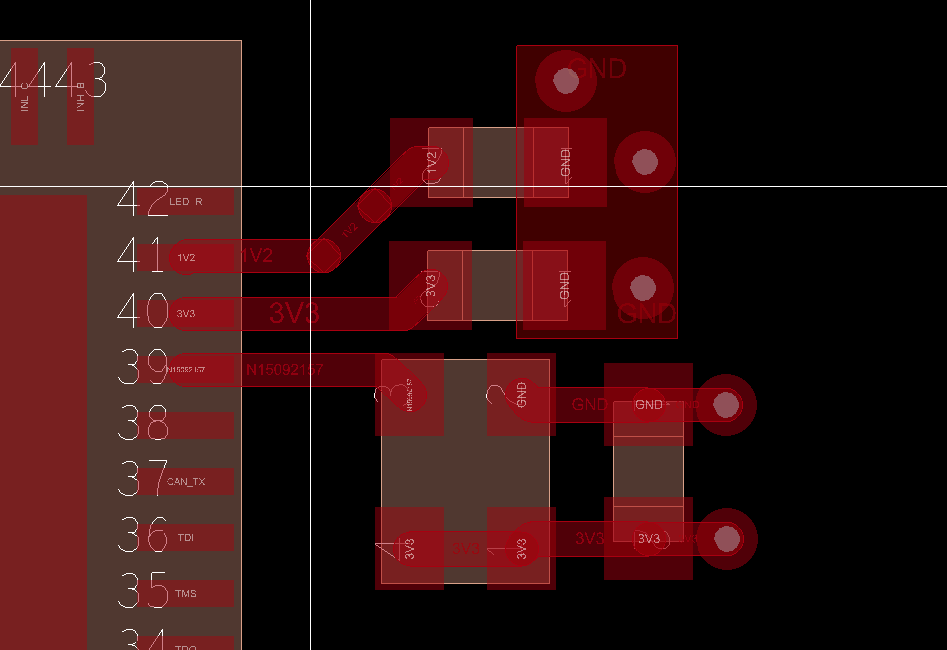

we are using F280049CRSHS uP and would appreciate some hints about routing Crystal Oscilator and decoupling caps.

Generally it seems the F280049CRSHS does not have comfortable pin arrangement in terms of placing decoupling caps - no GND pins adjacent to VDD/VDDIO.

What we did is to connect VDD pad of decoupling cap directly to pin and GND pad by via to thermal pad. Is that ok?

About Oscillator Connection - does it look good? - again pin arrangement does not facilitate to make guard GND ring around it.

thanks a lot in advance

have a great day

KR

Vincenzo