Part Number: TMS320F28377D

Hi Team,

My customer want to use SCI boot to program both F2837xD CPU1 and CPU2 flash on empty chip without application code by using the same SCI boot pin, it is no problem to do SCI boot at CPU1 according to boot pin setting, but for CPU2 without boot pin selection, how to do SCI boot when there is no bootloader code in CPU2 flash?

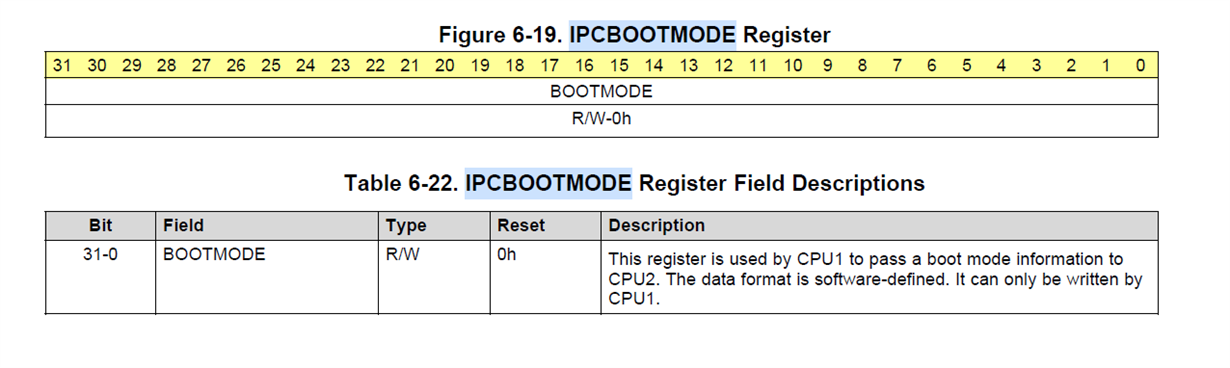

From the below diagram, I did not see how to choose the SCI boot mode for CPU2, only in EMU boot that use EMUKEY value to decide whether can use SCI boot. which is register that can be configured by CPU1 to choose boot mode for CPU2? it seems setting IPCBOOTMODE by CPU1 that can work, but I did not see more info about IPCBOOTMODE. what value in IPCBOOTMODE is corresponding to SCI boot for CPU2?