Hello,

I have a question regarding software triggered interrupts.

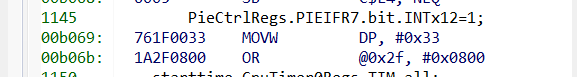

In my application I have used INT12 from group 7 to trigger an interrupt. This is an empty slot in the table (see picture).

This works fine.

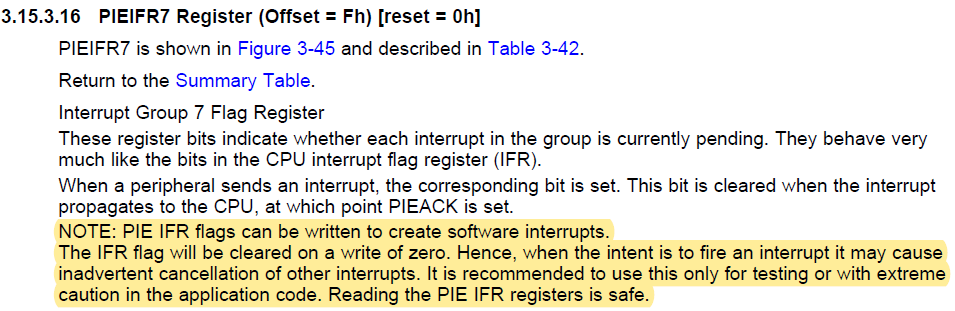

What happens if one interrupt from the peripheral (in this case the DMA) is issued at the same time when the c28x sets the bit 12 in PIEIFR7?

Is this interrupt omitted?

Thank you very much

Ralf