Other Parts Discussed in Thread: UNIFLASH

Hi,

my customer build a project and no error report.

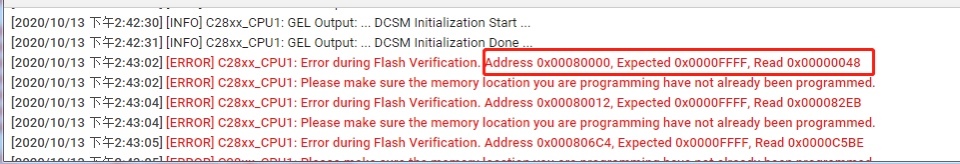

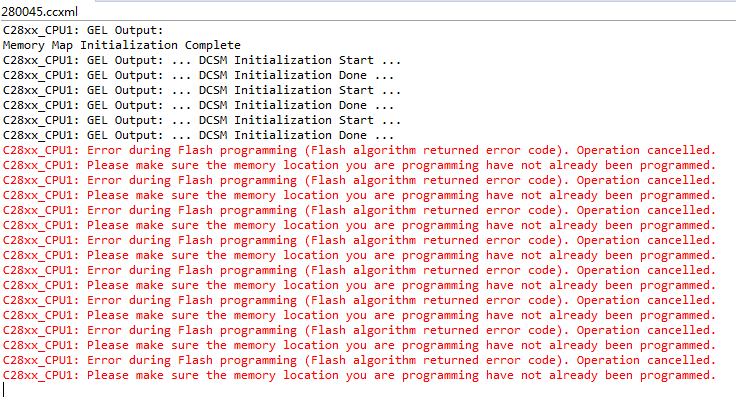

But when they load it on the board, the error is as below:

We are not sure if the problem is caused by the fact that we merge different flash sectors together as below in cmd file. But I believe it's okay to merge different sectors(from sector 0 to sector 15) into single space, right?

Then what may be the problem?