Hi Team,

I am trying to configure 280049`s ADC for my project. I have some doubts regarding the ADC acquisition window calculation explained in TRM. The following are my questions,

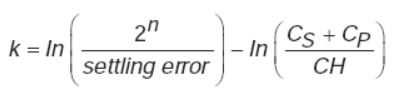

1. The settling error explained in the section 13.15.2 raises some doubts. It is said that the the sampling capacitor should be charged to 1/4 LSB or 1/2 LSB of final value. The LSB value of my ADC is around 0.000732V. So in the equation provided in the same section (given below) which value for settling error should I consider while evaluating the equation. If settling error is 1/4 LSB should I use 1/4 LSB or 0.000183 (= 0.000732 / 4) ?

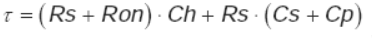

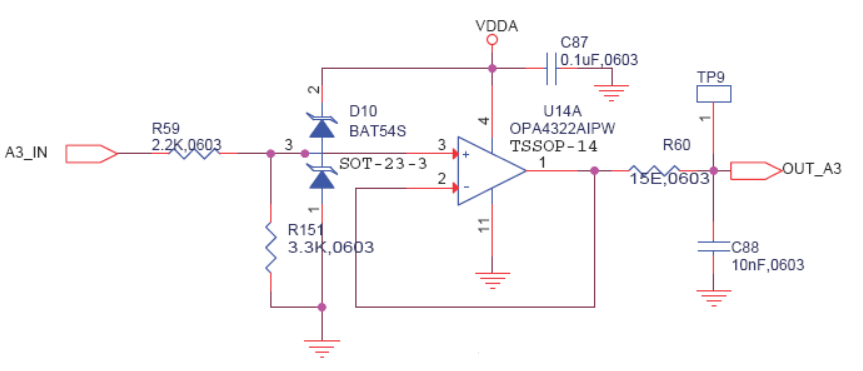

2. How to calculate values Cs and Rs in the following equation for my ADC driving circuit given below ,

I considered Cs as 10 nF and Rs as 15 ohms, is this assumption is correct?

3. Is this ADC is capable of double ended single inputs or single ended only ?

4. Will it cause any problem to simultaneous sampling, if I use different channels with different Cp values leading to different ACQPS value. If that is the case is the EOC generation will be at the end of the conversion of channel with largest SH + acquisition window ?

5. If ADC sampling is controlled by SOC which is in turn generated using ePWM in my application, I wonder what is the importance of ADCCLK in sampling ? Do I need to choose a specific value for ADC clock, according to each circuit. If yes, what will be the criterion for choosing the ADC clock for a specific application?

Best Regards,

Vineeth N