C2000 Team,

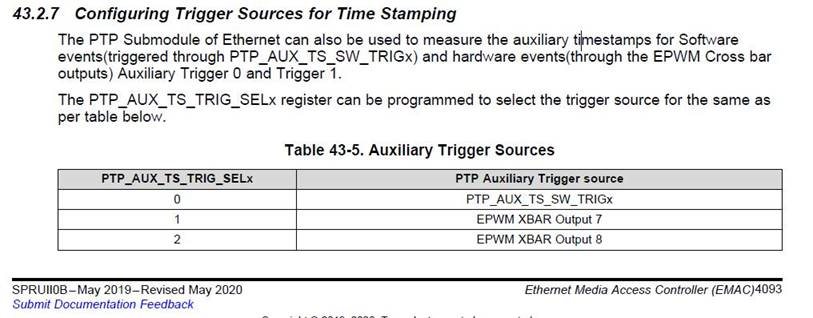

On F28388D a customer is using the AUX_Timestamp feature of the ethernet in the Cortex-M. They are triggering this using EPWM XBAR Output 8.

EPWM XBAR Output 8 is being fed from INPUTXBAR4, which in turn is being fed from GPIO95. GPIO95 in turn is being fed from a CLB output. Yes, very routing heavy! The configuration code for this is:

XBAR_setCLBOutputMuxConfig (CLBOUTPUTXBAR_BASE,XBAR_OUTPUT5, XBAR_OUT_MUX06_CMPSS4_CTRIPOUTH_OR_L);

XBAR_enableCLBOutputMux(CLBOUTPUTXBAR_BASE,XBAR_OUTPUT5,XBAR_MUX06);

GPIO_setPadConfig(95, GPIO_PIN_TYPE_STD); // GPIO95 is pin

GPIO_setDirectionMode(95, GPIO_DIR_MODE_OUT);

GPIO_setPinConfig(GPIO_95_CLBOUTPUTXBAR5 );

XBAR_setInputPin(INPUTXBAR_BASE,XBAR_INPUT4,95); //Set GPIO95 to Input XBar4 for combined trip input

XBAR_setEPWMMuxConfig(XBAR_TRIP8, XBAR_EPWM_MUX07_INPUTXBAR4 ); /* GPIO95 is connected to INPUTXBAR4, pass this signal to EPWM XBAR Output 8 */

XBAR_enableEPWMMux(XBAR_TRIP8,XBAR_MUX07); /* This signal will be used to trigger a PTP time stamp on CM */

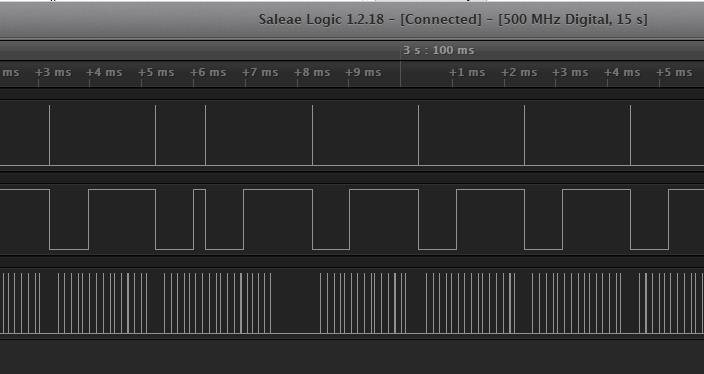

Things appear to working like this, EXCEPT that the timestamp is triggering off the falling edge of GPIO95. Here is a logic analyzer screen shot:

The top trace is the Aux Timestamp and middle trace is the GPIO95.

PROBLEM: We need the timestamp to trigger off the rising edge of GPIO95 (which again, is EPWM XBAR Output 8). Assuming the timestamp always triggers on a falling edge of the trigger signal, we need to invert the signal to produce the proper timing.

THINGS WE'VE TRIED:

1) Inverting the trip polarity: EPwmXbarRegs.TRIPOUTINV.bit.TRIP8 = 1;

2) Inverting the GPIO95 at the GPIO input using GPyINV register.

3) Inverting the signal in the CLB (prior to the routing to GPIO95).

None of the above seemed to have any effect.

We've checked for EALLOW issues, and confirmed using CCS that the registers are configured as expected.

We know the timestamps are triggering from GPIO95 because if we change the INPUTXBAR4 select to 0 instead of 95, there are no cortex-M timestamps (which means no triggering off of the signal).