Hi,

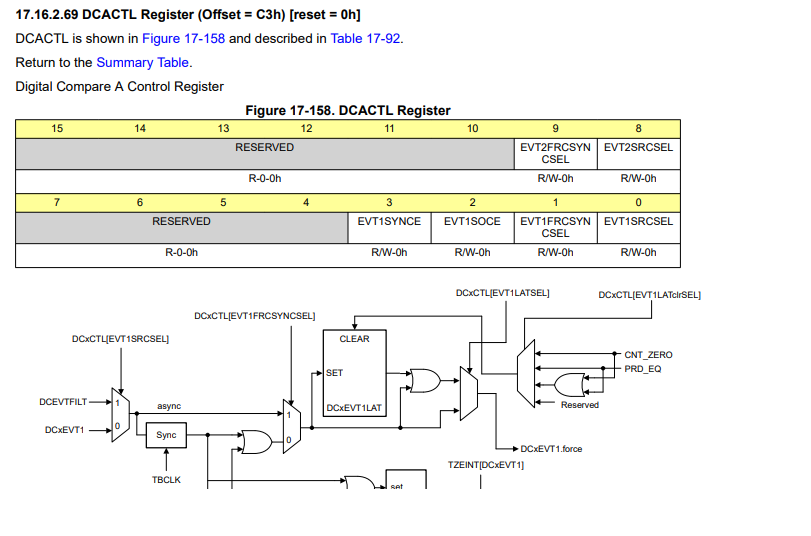

I am trying to use F280025C Control Card, ePWM Digital Control module. In the block diagram it is shown that there are options present in DCxCTL register to latch (EVTyLATSEL]) or clear (EVTyLATclrSEL]) the Digital compare event (DCxEVTy). But I do not see the same options in the register description as shown below. Can you let us know about this and how to make use of it?

Thanks,

Aditya