Part Number: TMS320F28033

Other Parts Discussed in Thread: UCD3138

Tool/software: Code Composer Studio

Hi,

We have included TMS320F28033PAG in our design to control an H bridge (four IGBT:s)

This is a frequency controlled LLC bridge

This is done by using two main output PWMs with one shadow PWM each that runs 180 degrees phase shifted with dead time.

However, we see problem with one of the PWMs (main and shadow) when phase shifting it compared to the other main PWM

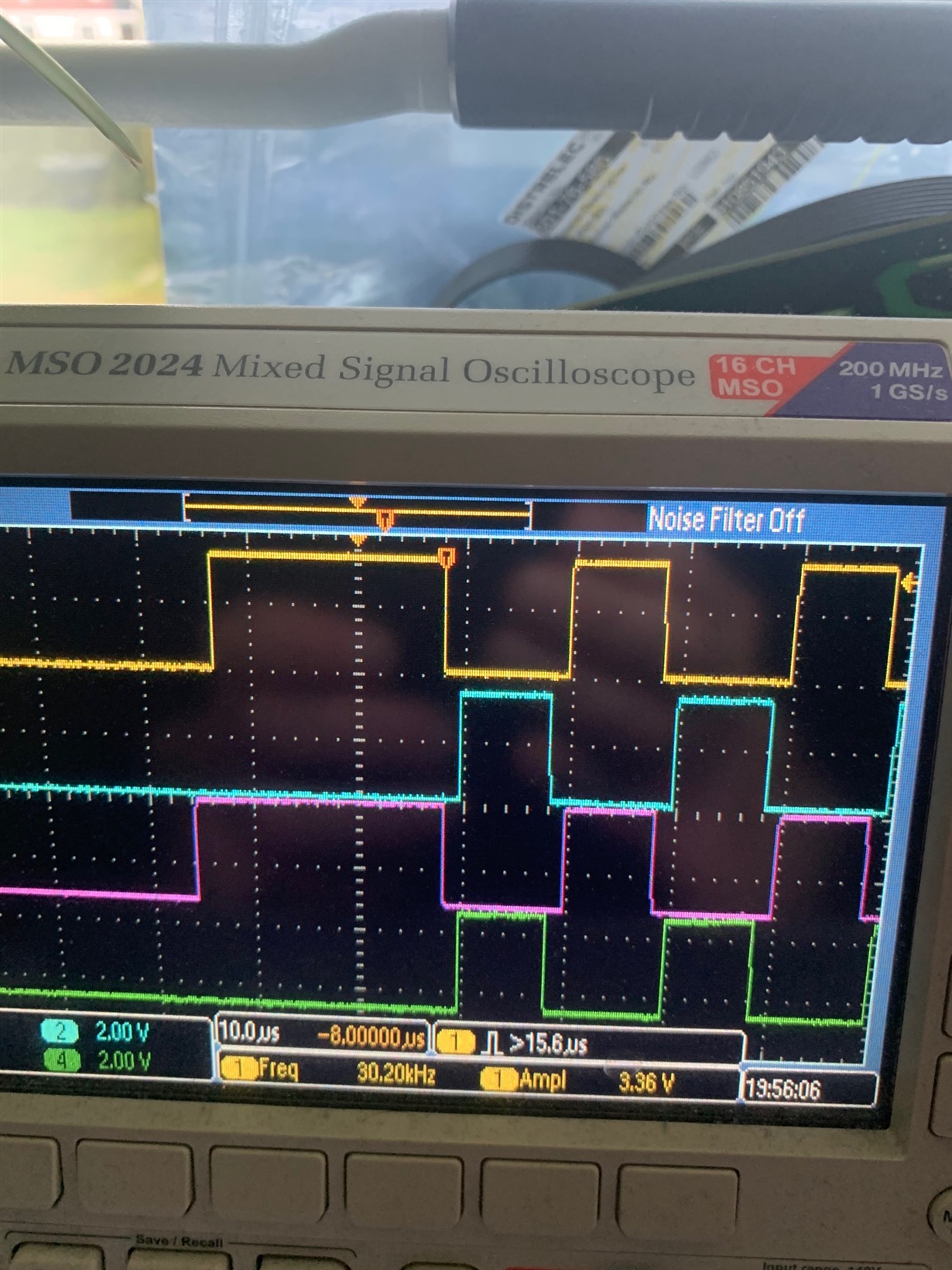

Of we have zero on phase shifting at start (TBPHS=0) we see a missing pulse when starting to increase the phase shift to a very small value, see picture below

If we start the pwm set with a very small phase shift (TBPHS = 0.001) at initialization we see the missing pulse directly when the microcontroller starts to generate pulses at the PWMs, see picture below

We do not want to see any missing pulses.

Is this possible to perform?

See the init setup of the PWMs below

Are we using this in a incorrect way?

Thank you

Best regards

John

EPwm1Regs.TBCTL.bit.PRDLD = TB_IMMEDIATE; //TB_SHADOW;

EPwm1Regs.TBPRD = (MD_DRIVER_PERIOD_CYCLES - 1);

EPwm1Regs.CMPA.half.CMPA = (MD_DRIVER_PERIOD_CYCLES / 2); // 0;

//EPwm1Regs.CMPA.half.CMPA = 0; // No pulses

EPwm1Regs.TBPHS.half.TBPHS = ZERO_PHASE_SHIFT;//0; // Set phase register to 0

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; // Count up

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; // Master module

EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO;

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1; // No prescaler

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_PRD; //CC_CTR_ZERO;

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_PRD; //CC_CTR_ZERO;

EPwm1Regs.AQCTLA.bit.ZRO = AQ_SET;

EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR;

EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; // Deadband enabled

EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; // Activate complementary B-channel

EPwm1Regs.DBCTL.bit.IN_MODE = DBA_ALL; // EPWMxA is the source for both falling- and rising-edge delays

EPwm1Regs.DBRED = DRIVER_RISING_EDGE_DELAY_CYCLES; //counter clocked by system clock 60MHz

EPwm1Regs.DBFED = DRIVER_FALLING_EDGE_DELAY_CYCLES;

//////////////////////////

// PWM 2

EPwm2Regs.TBCTL.bit.PRDLD = TB_IMMEDIATE; //TB_SHADOW;

EPwm2Regs.TBPRD = (MD_DRIVER_PERIOD_CYCLES - 1);

EPwm2Regs.CMPA.half.CMPA = (MD_DRIVER_PERIOD_CYCLES / 2); // 0;

//EPwm2Regs.CMPA.half.CMPA = 0;

EPwm2Regs.TBPHS.half.TBPHS = ZERO_PHASE_SHIFT;//0; // Set phase register to 0 initially

EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; // Count up

EPwm2Regs.TBCTL.bit.PHSEN = TB_ENABLE; // Slave module

EPwm2Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; // Sync

EPwm2Regs.TBCTL.bit.CLKDIV = TB_DIV1; // No prescaler

EPwm2Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;

EPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_PRD; //CC_CTR_ZERO;

EPwm2Regs.CMPCTL.bit.LOADBMODE = CC_CTR_PRD; //CC_CTR_ZERO;

EPwm2Regs.AQCTLA.bit.ZRO = AQ_SET;

EPwm2Regs.AQCTLA.bit.CAU = AQ_CLEAR;

EPwm2Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; // Deadband enabled

EPwm2Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; // Activate complementary B-channel

EPwm2Regs.DBCTL.bit.IN_MODE = DBA_ALL; // EPWMxA is the source for both falling- and rising-edge delays

EPwm2Regs.DBRED = DRIVER_RISING_EDGE_DELAY_CYCLES;

EPwm2Regs.DBFED = DRIVER_FALLING_EDGE_DELAY_CYCLES;