HI Team,

We are using the DMA to generate the required number of PWM cycles and have issue with ONESHOT, When ONESHOT is disabled its not waiting for the event so unable to count the number of PWM cycles.

- We need to start the PWM on the ECAP interrupt, As ECAP cannot trigger the DMA, First we are triggering DMA with Software force bit is set (DmaRegs.CH1.CONTROL.bit.PERINTFRC = 1).

- Here only one word (1 Burst of length 1 word ) will be transferred.

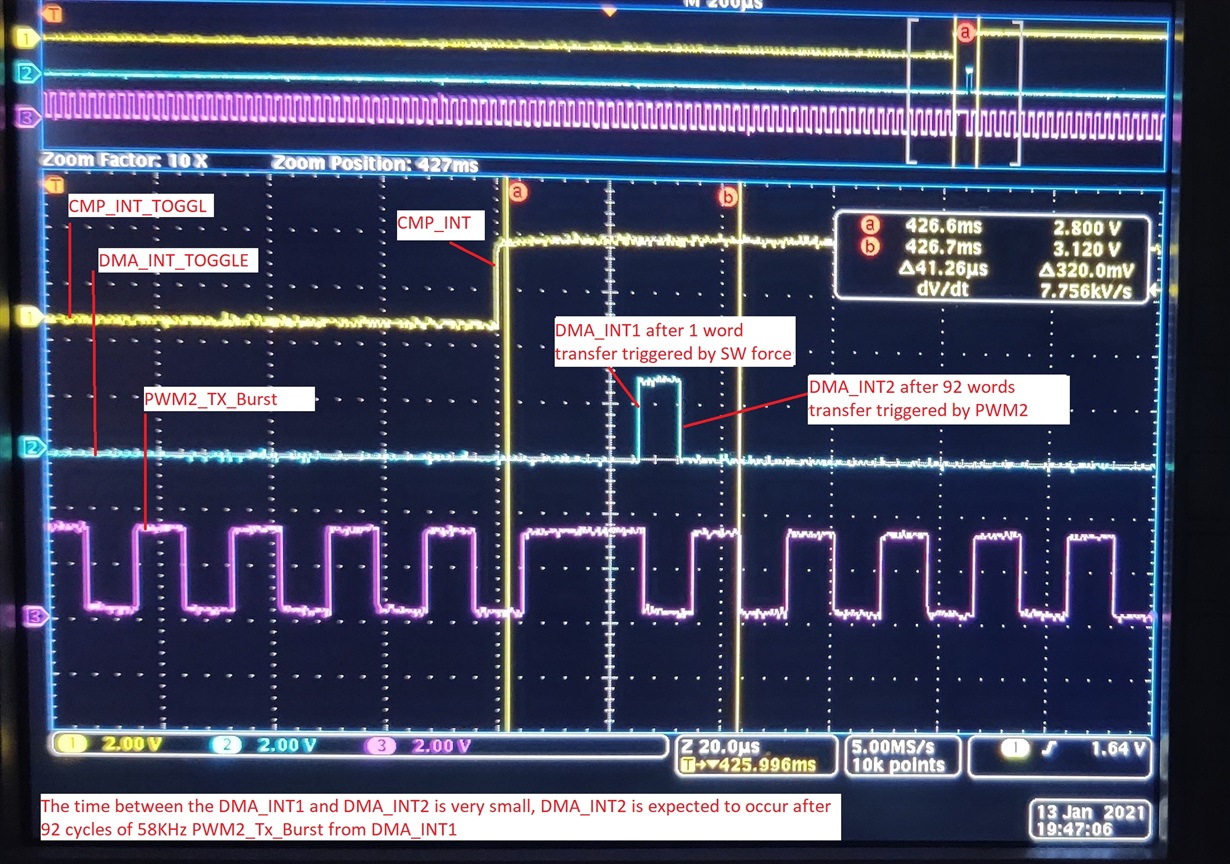

- DMA transfer is completed and DMA interrupt is generated as shown in the diagram below. (DMA interrupt is generated at the end of the transfer).

- In the DMA_ISR, Initialize the DMA to trigger from the EPWM2SOCA on every CTR = PRD and start the transfer for 92 word (Burst length is 1 word, Total 92 transfer).

- The ONESHOT bit (DmaRegs.CH1.MODE.bit.ONESHOT = 0) is not set so DMA should wait for Peripheral trigger (From PWM2 ADCSOC when CTR = PRD) after each transfer.

As you see in the diagram, After first DMA Interrupt(DMA_INT1) one word is getting transferred and after 2nd interrupt (DMA_INT2) remaining 92 words are transferred but the transfer is not happening on every PWM cycle, All 92 words are transferred on single PWM event, Seems it’s not waiting for trigger after each transfer.

Please let me know if you need more details, Please test ONESHOT bit at your end and confirm.

Thanks,

Ajay