Part Number: TMS320F28388D

Other Parts Discussed in Thread: TINA-TI

Hi

I'm testing 28388 ADC with adc_ex5_soc_continuous example.

Circuits based on control card, Using REF5030 for reference.

I connected two 1Kohm between ADCINB0 - GND, ADCINB0 - 3.3V to get 1.65V

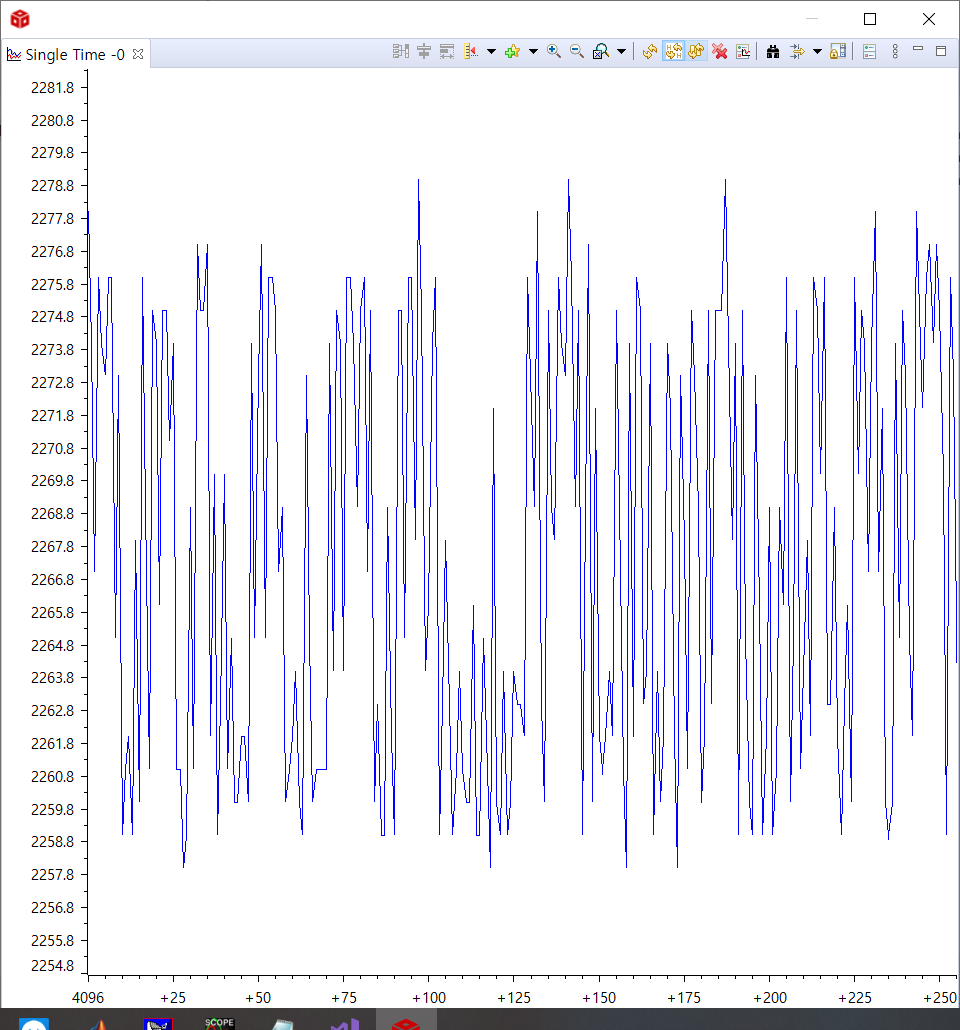

Here is the sample result, about 20 LSB fluctuation.

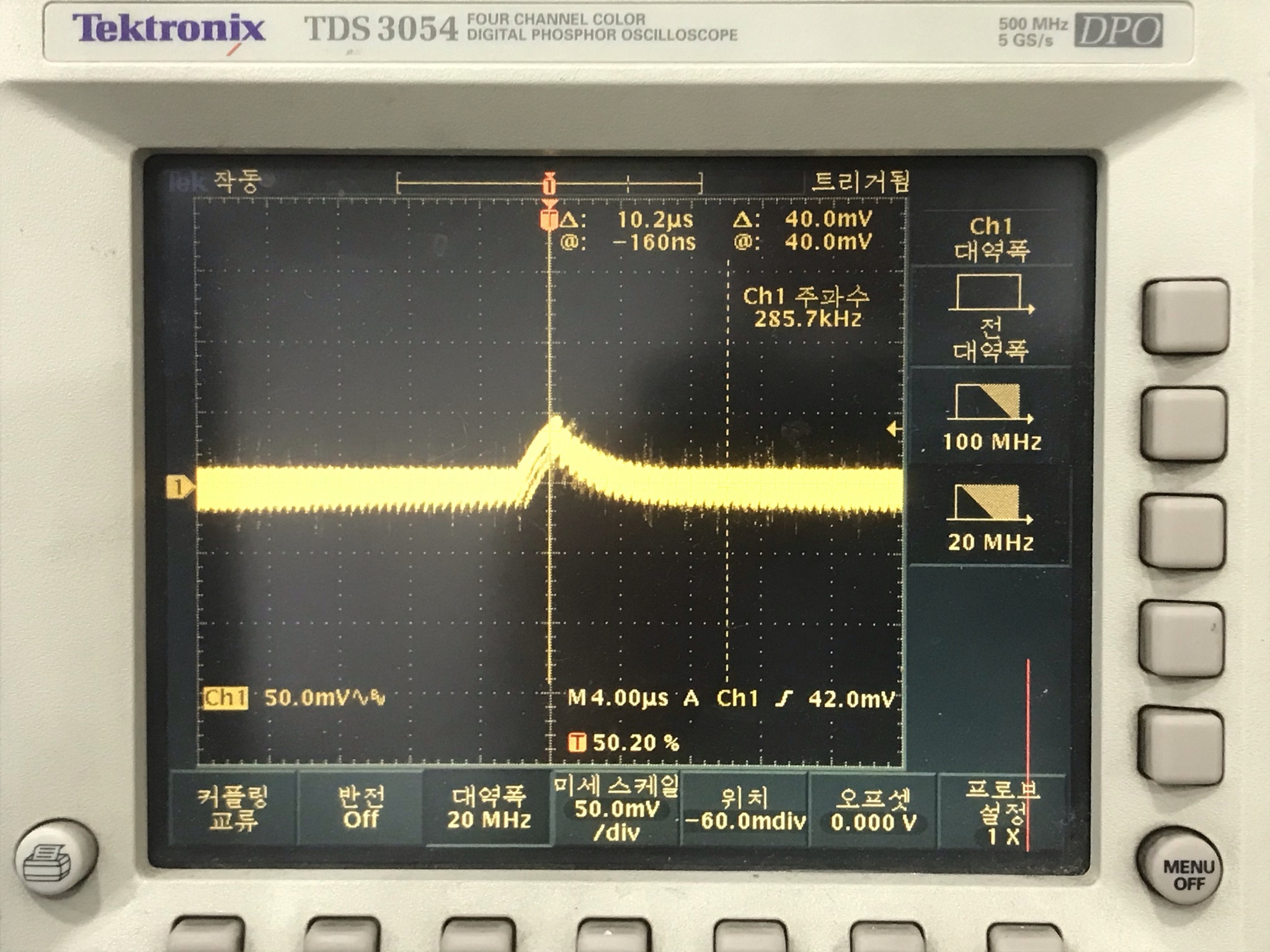

But I wonder why ADCIN PIN jump 50mV on oscilloscope

when it sample. while 3.3VA & ref pin still clean on oscilloscope.

I tried several acqps 8 / 63 / 125. 125 looks good, but only 8 gets less than 9 LSB flux, while the other 20 LSB.

Is it predictable normal phenomenon?

Is there any method that can improve it?

Regards

Kim taeyeong