Customer do function like below step

1, CPU1 initialize the EMIF1 and configurate the CPU2 as master for EMIF1.

2, CPU1 put data into Global Ram and send notice to CPU2 by IPC

3, if CPU2 check IPC flag, then read the data from Global Ram and write data into EMIF1 in main loop or other interrupt function => data can read and write ok

4, if CPU2 respond IPC interrupt, then read the data from Global Ram and write data into EMIF1 in IPC interrupt => data read ok but write fail

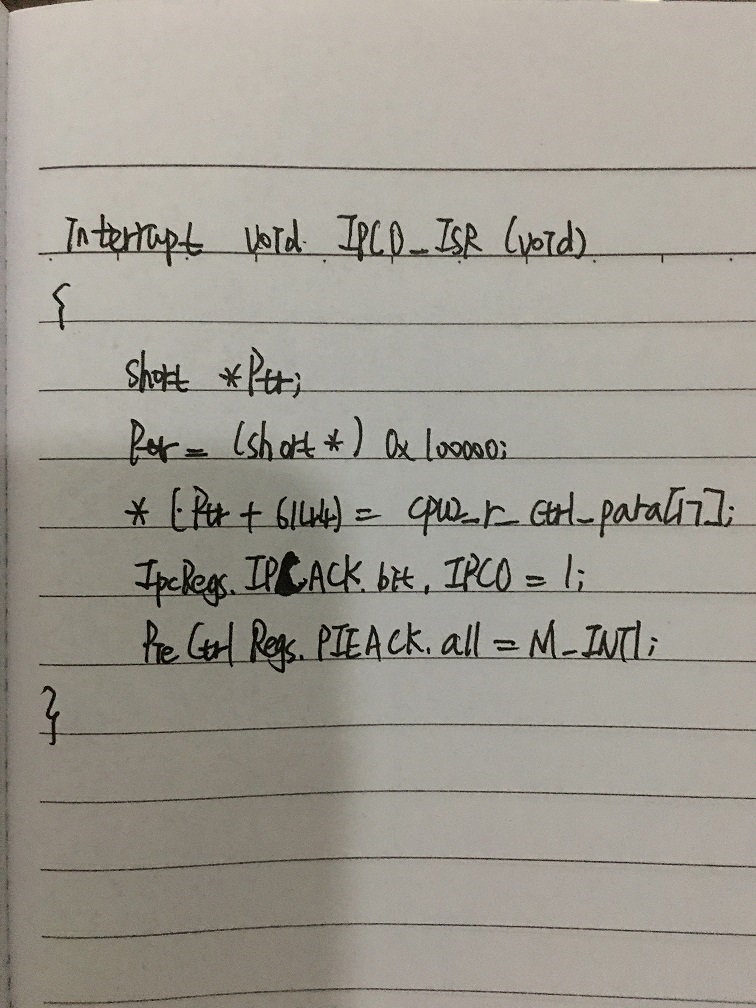

May I ask if EMIF write behavior has any limitation or conflict with IPC interrupt function? Below is customer code for EMIF operation in IPC interrupt, does any operation wrong?