Part Number: TMS320F28375S

Other Parts Discussed in Thread: TMS320F280049C

Hi,

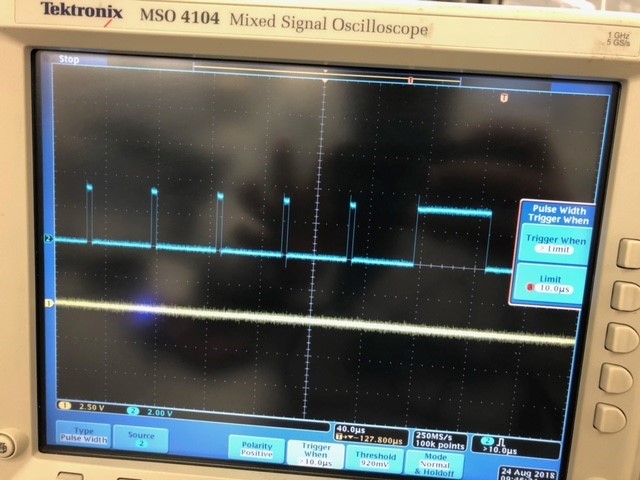

I have a strange problem in the ePWM module. I see a glitch in the PWM waveforms when there is a jump in compare value from less than max counter to greater than max counter.

ePWM configuration:

Up-Down Counter mode

ePWM clock 100MHz

Max period: 2500 (This gives me a pwm frequency 20KHz)

PWM outputs: Active low complementary

I did a test with PWM running at constant duty cycle with compare value 2450, and then manually updated the compare value to 2550. I could see a glitch on the signal.

Screetshot below.

Another test was done with PWM running at constant duty cycle with compare value 2450 and then going up in smaller steps like 2480, 2499, 2500, 2501 and 2550. I did not see glitch on the signal.

I tried this on different PWM modules, the results were same. So is this a bug in the module?

CCS Version 10.1

I have seen few posts in e2e forum about the ePWM glitch, but I think my problem was not part of that.

Thank you.