Other Parts Discussed in Thread: ADS8684, ADS8684A

Hello everyone,

I am working on a project with a F28379D, I have a project with all peripherals that I need (PWM, ADC...) and I am currently designing the SPI communication to use an external ADC (ADS8684).

I designed all the function that I need and my SPI seems to be OK (I don't have the ADS8684A yet so I just look the signals of the SPI bus with an Oscilloscope).

To optimize my code I wanted to see where do I loose time calculation in the program. I did some test and the fact is that my SPI is taking a lot of time...

Here is my problem :

I don't understand why I have more than 500ns beetween my instruction GPIO_WRITE(32,0), and my SPI_writeData...

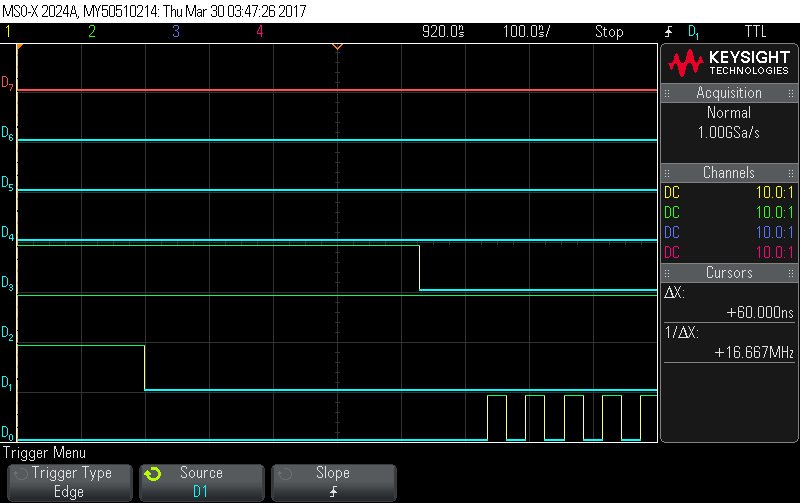

Here is a capture of my oscillo ( D0 is the CLK signal of the SPIA; D1 is GPIO 32; D3 is the CS signal of the SPIA)

Here is my instruction :

And here is the configuration of my SPIA :

I precise again that my SPI is connected to nothing for the moment, I don't think that's the problem but I precise it...

Thank you in advance for your answer !

Guillaume