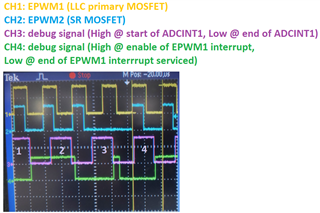

EPWM1 interrupt = used to updated EPWM1&2 parameters; shadowed; triggered by EPWM1 count = CAU;

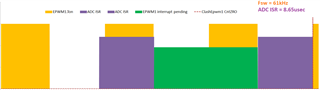

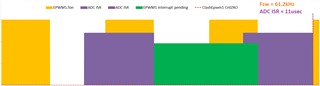

I am encountering problems when the EPWM1 interrupt remains pending when the ADCINT1 interrupt gets serviced on its next ADC cycle.

The problem manifests as EPWM1 and/or EPWM2 parameters not updated correctly at the same time.

I have played around with different EPWM1 settings and the problem persists.

I want to use it to clear the pending EPWM1 interrupt at the start of ADCINT1 routine.

But...

1) Does implementing Rule#1 solve my problem?

2) Do you have an example on how to implement it?

3) Can the EPWM1 interrupt's PIEIFR be cleared while inside ADCINT1?