Hello,

I'm working on a project where I need phase shifted PWMs. Right now I'm using HRPWM on all the modules from EPWM1 up to EPWM8. EPWM1 is the master which generates a SYNC signal when CTR = ZERO. The phase shift of the master is of course fixed to 0°. For all of the other modules I need smooth phase-shift transitions between 0° and 180°.

Let me further explain how I configured my EPWM modules. I'm using up-down-count on all modules. The MCU is running at 90MHz and the TBPRD is set to 450 which equals a frequency of 100kHz. I can't use the deadband module because I'm using HRPWM, so I'm using CMPA and CMPB for creating a deadtime. For example the dead-time is 200ns. That means that EPWM1 has a CMPA and CMPB of 234 and EPWM2 a CMPA and CMPB of 216. The other modules are configured the same way.

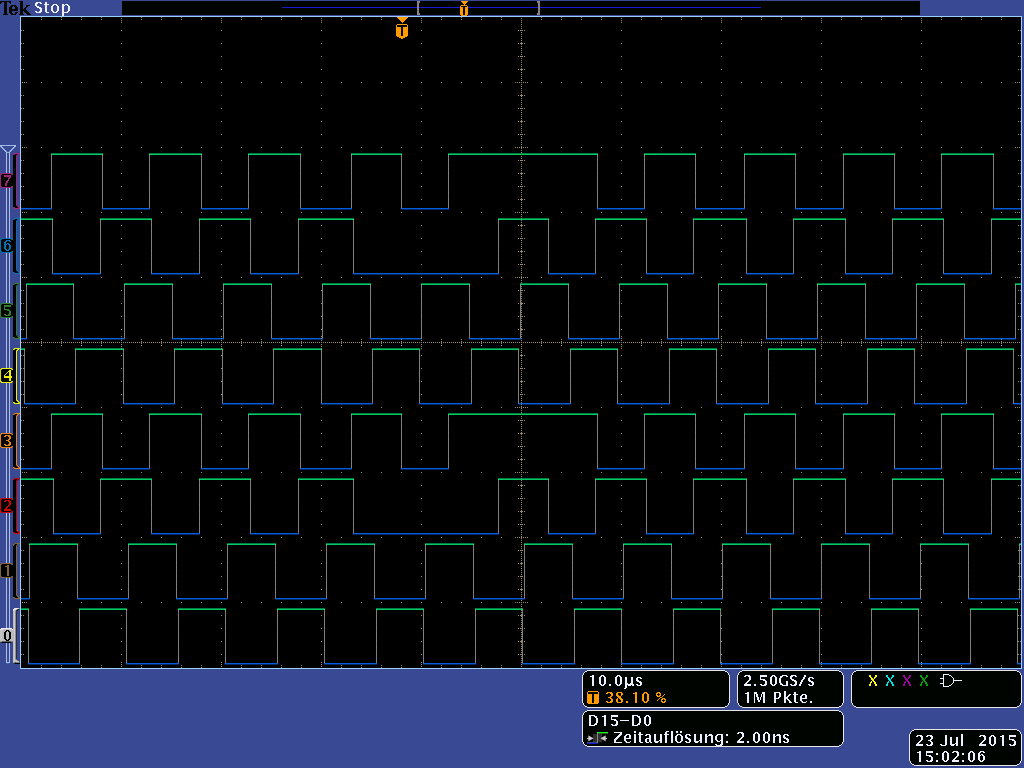

Now begins the problem. When I'm raising my phase shift and come to the two critical points of TBPHS = 216 or 243 the PWM jumps a compare event and the signal is completely screwed up. You can see it here in this picture:

This PWM signal will result in a shoot-through and kill the MOSFETs.

I tried to force a compare event when this happens and it kind of works. I force both signals to high (the PWM will be inverted externally), so a shoot-through will not happen. But that is not good enough. The signal still is completely screwed up and practically unusable.

So...is there an elegant way to solve this problem? Only using up- or down-count method doesn't work either. The cause of the problem are the 2 cycles delay between master and slave PWM modules (at least I think), so it won't really go away with another count method.

Thanks