Part Number: TMS320F28379D

Other Parts Discussed in Thread: CCSTUDIO, CONTROLSUITE, TMS320F28075

Tool/software: Code Composer Studio

Good morning.

I notice some problem when I'm using CLA1 after CPU1 configuration. I use CCStudio 7 with TI v6.4.2 Compiler on F28379D target [TI v16.9.1.LTS makes a lot of #2638 error: The alignment

of an array element is greater than the element size].

Anyway, my simple test code follows a TI sketch but it sets only Task1 on CLA for easily changing a local CLA variable. The compilation steps are ok; also debug steps

improve correctly.

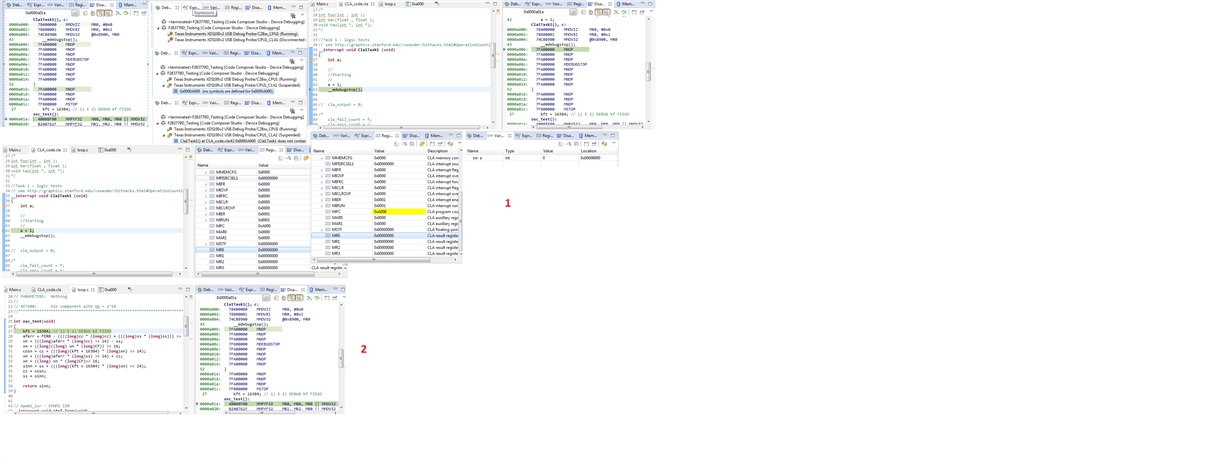

When I starting CPU1 code, after that I connect in debug window either CPU1/CLA1, CPU1 executes own code upto waiting in Cla1ForceTask1andWait() function: CPU1 state

is in Running mode while focus pass on CLA1 that is in Suspended mode with no symbols defined for 0x0000A000 [I know is the origin LS4-LS5 RAM assigned to CLA1 by

2837xD_RAM_CLA_lnk_cpu1.cmd]. Finally, when I load symbols on CLA1, it stops in the first C istruction that is 'a = 1'.

Follow it is the assembly code with one istruction over MSTOP.

Cla1Task1(), c:

0000a000: 78400000 MMOVIZ MR0, #0x0

0000a002: 78800001 MMOVXI MR0, #0x1

0000a004: 74C08900 MMOV32 @0x8900, MR0

43 __mdebugstop();

0000a006: 7FA00000 MNOP

0000a008: 7FA00000 MNOP

0000a00a: 7FA00000 MNOP

0000a00c: 7F600000 MDEBUGSTOP

0000a00e: 7FA00000 MNOP

0000a010: 7FA00000 MNOP

0000a012: 7FA00000 MNOP

0000a014: 7FA00000 MNOP

52 }

0000a016: 7FA00000 MNOP

0000a018: 7FA00000 MNOP

0000a01a: 7FA00000 MNOP

0000a01c: 7F800000 MSTOP

27 kft = 16384; // 1) E 2) DEBUG kf FISSO

osc_test():

0000a01e: 40008F00 MMPYF32 MR0, MR0, MR0 || MMOV32 @0x8f00, MR0

The questions are relative the follow event:

1) If I execute a single step, MPC arrived in 0x000a006 while the blue arrow pointed __mdebugstop() function. MR0 register would be changed in 1 value and then it will

be loaded in 0x8900 that is CLA1 Data RAM assigned for 'a' variable. If I check MR0,'a' in Variable window and 0x8900 RAM location, I don't see any right value [it

preserves 0 value]. However, If I manually change value in a Variable window or in Memory, it changes correctly. It seems that CLA have some problem with memory

control but also with own MR0 register [???];

2) If I continue with two steps, MPC overruns MSTOP CLA istruction and reaches 0x000a01e program location that it would be assigned to CPU1 code [???].

Is there somebody that clarify this behavioral ? Thank's a lot.

Diego.

PS: I apologize cause my bad english.