Part Number: TMS320F28075

Other Parts Discussed in Thread: TMS320F28035

Hi everyone,

I'm encountering a problem with HRPWM similar to the one mentioned in this topic. I have seen it occur both on TMS320F28035 (ePWM Type 1) and TMS320F28075 (ePwm Type 4).

The problem manifests itself as an unwanted glitch on the PWM output. In the actual application I use many peripherals such as the ADC, ECAP, ECAN, SPI, CPU timers and interrupts, CLA, etc. but I took some time to find the smallest possible code which allows me to reproduce the problem, which seems to only involve the ePWM peripherals.

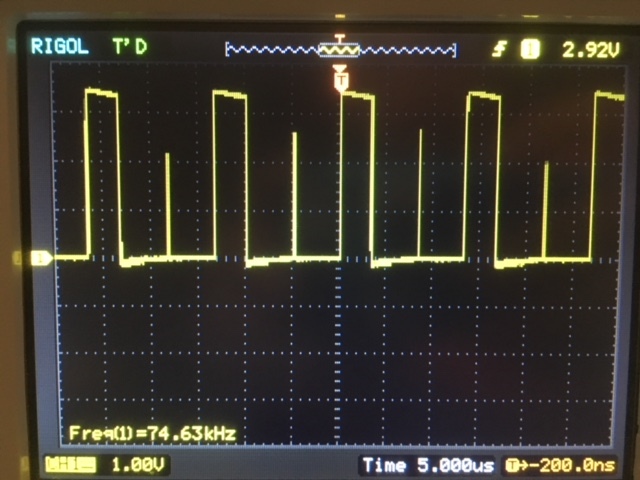

The oscilloscope screenshot below shows the glitch. It is achieved with a small program running on the TMS320F28035 controlCARD.

The yellow signal is EPWM1A on GPIO0. The blue signal is a reference signal generated using EPWM2A with edges configured for events CTR=PRD and CTR=ZRO.

First a few notes on things I have tried:

- The ePWM period (TBPRD) and clock speed (TBCTL[CLKDIV] and TBCTL[HSPCLKDIV]) do not seem to have any influence on the problem.

- I have tried with and without using the autoconversion feature, it doesn't seem to change anything to the problem.

- I have tried with and without the background calibration of the MEP using the SFO() function and doesn't seem to change anything to the problem.

- I have tried using the internal oscillator and an external quartz but it doesn't change anything to the problem.

The code used to reproduce the problem is the following:

EALLOW;

SysCtrlRegs.PCLKCR1.bit.EPWM1ENCLK = 1;

SysCtrlRegs.PCLKCR0.bit.HRPWMENCLK = 1;

EPwm1Regs.TBCTL.bit.CTRMODE = 2;

EPwm1Regs.AQCTLA.bit.CAU = 1;

EPwm1Regs.AQCTLA.bit.CAD = 2;

EPwm1Regs.TBPRD = 200;

EPwm1Regs.CMPA.half.CMPA = 50;

EPwm1Regs.CMPCTL.bit.LOADAMODE = 1; // load on CTR = PRD

EPwm1Regs.HRPWR.bit.MEPOFF = 0;

EPwm1Regs.HRCNFG.bit.EDGMODE = 2;

EPwm1Regs.HRCNFG.bit.HRLOAD = 1; // load on CTR = PRD

GpioCtrlRegs.GPAMUX1.bit.GPIO0 = 1;

SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 1;

EDIS;

for (;;) {

DELAY_US(10);

EPwm1Regs.CMPA.half.CMPAHR = 0;

DELAY_US(10);

EPwm1Regs.CMPA.half.CMPAHR = (200U << 8);

}

All this program does is switch CMPAHR between zero and a non-zero value.

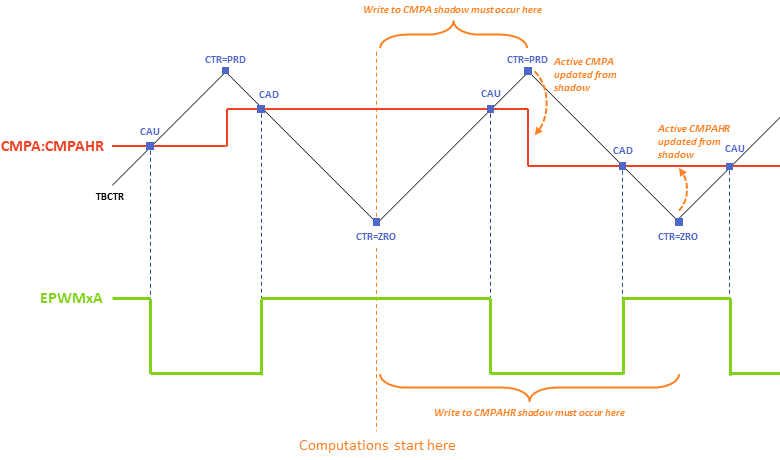

The problem only seems to appear when the ePWM is running in up-down count (TBCTL[CTRMODE] = 2) AND the micro-edge position logic controls the falling edge (HRCNFG[EDGMODE] = 2) AND the CMPAHR load event is programmed outside of the pulse (when the PWM signal is at 0).

This last condition is because I have seen the problem in two configurations:

- Pulses centered on CTR=ZRO (AQCTLA[CAU] = 1 / AQCTLA[CAD] = 2 / HRCNFG[HRLOAD] = 1)

- Pulses centered on CTR=PRD (AQCTLA[CAU] = 2 / AQCTLA[CAD] = 1 / HRCNFG[HRLOAD] = 0)

Furthermore the width of the glitch seems to be related to the value of CMPAHR, as shown by the two pictures below. The first one is with CMPAHR set to 130 steps and the second one with CMPAHR set to 230 steps.

That is all the information I have for now, but if you need to know anything else please let me know.

Cheers,

Pierre