Part Number: TMS320F28375S

Other Parts Discussed in Thread: AMC1303E2520, AMC1306E25, AMC1303M2520

Hi,

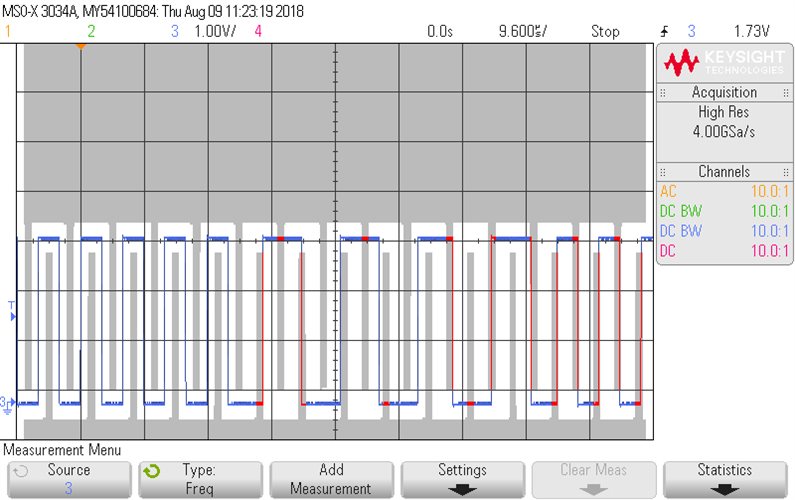

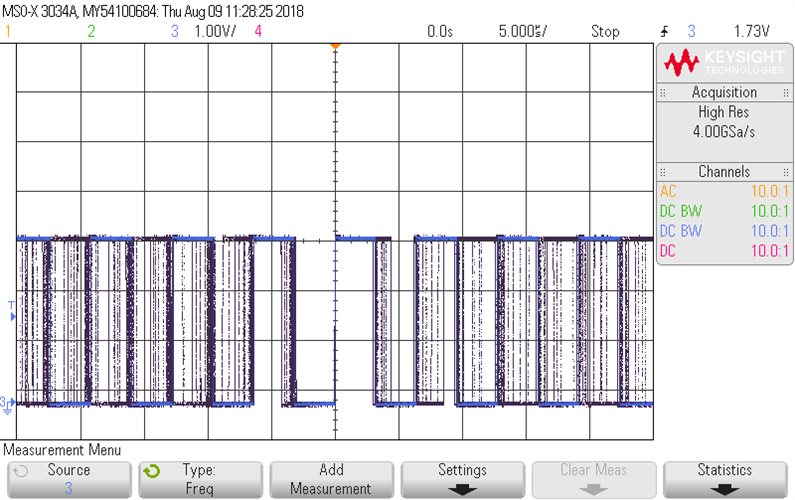

I have a 3 phase PFC application. I measure 3 phase currents, 3 phase voltages, dc voltage and dc current. The 3 phase voltages are "smooth" 50Hz, the 3 phase currents have high frequency ripple on them and dc voltage/current are also smooth and slow changing.

For measuring hardware I have: 5x AMC1303E2520: Manchester coded internal clk (for phase voltages and dc) and 3x AMC1306E25: Manchester coded externally clocked together by 20 MHz oscilator(for phase current). This is so that the current that has a high rate of change is sampled together and is totally synchronised.

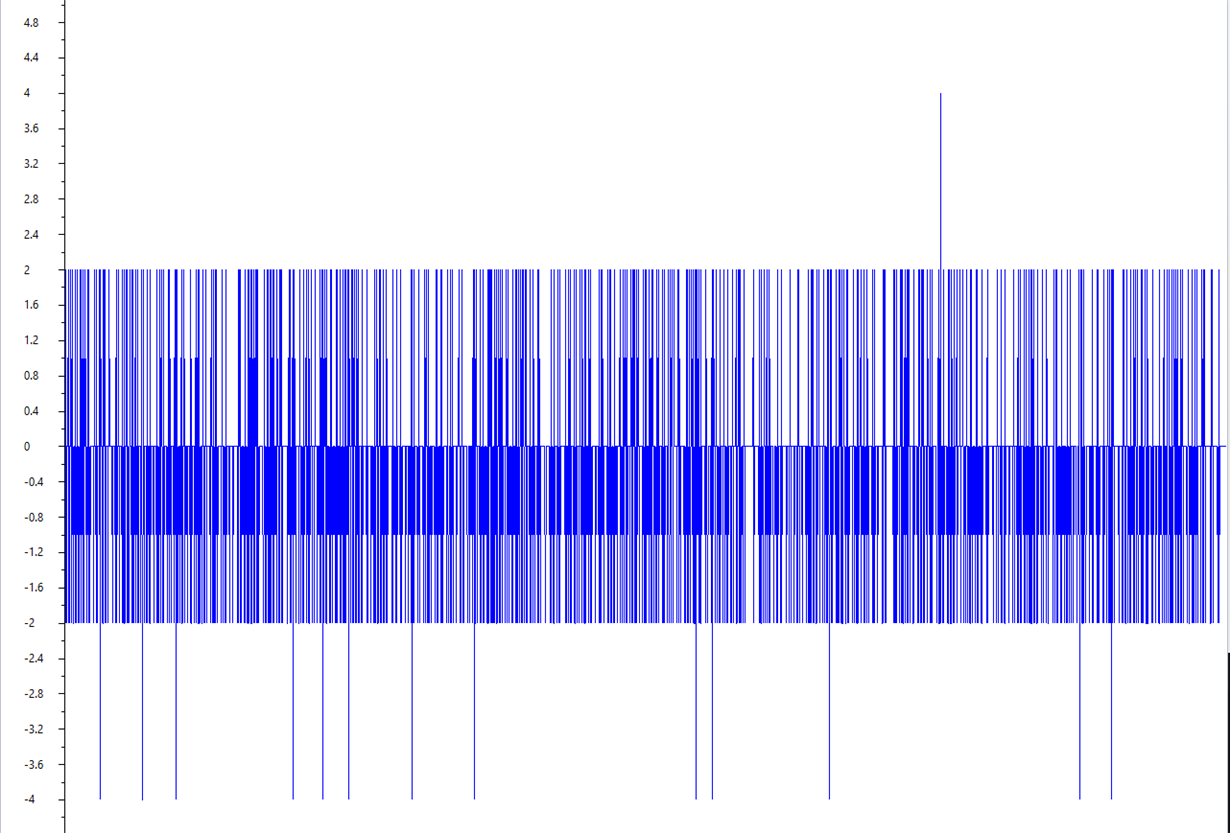

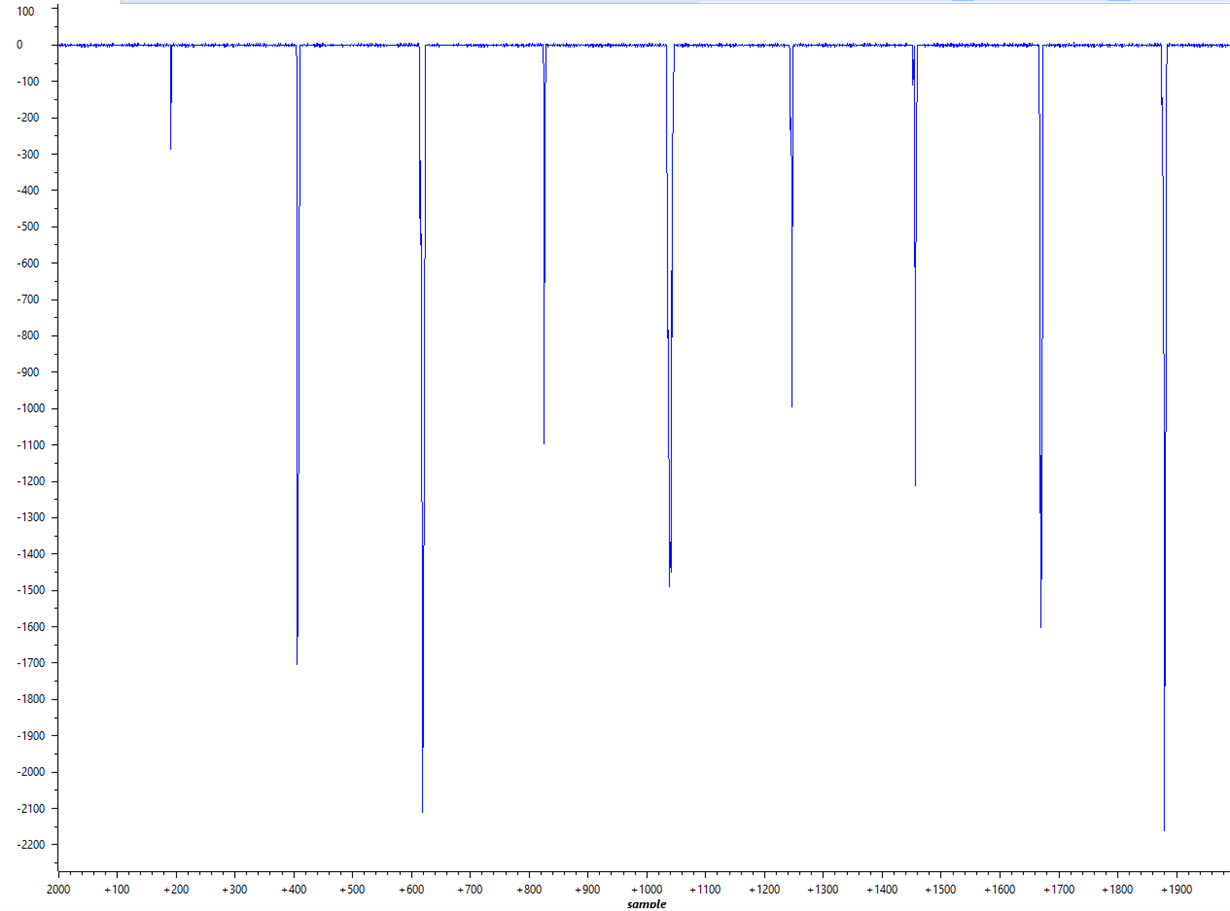

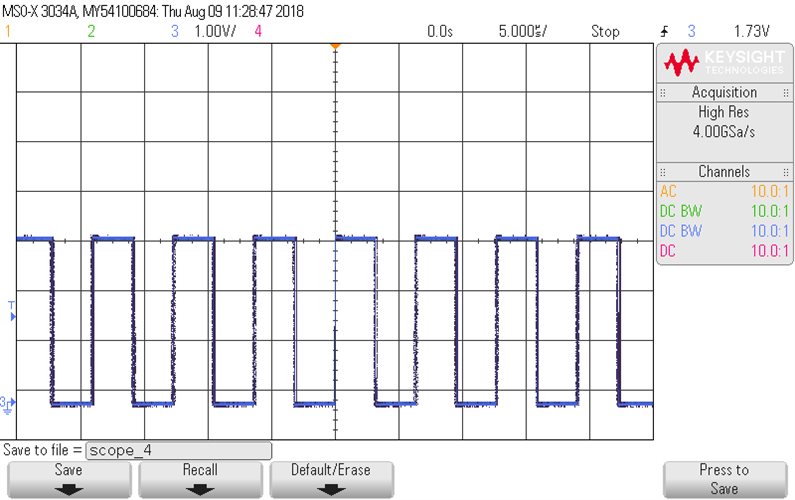

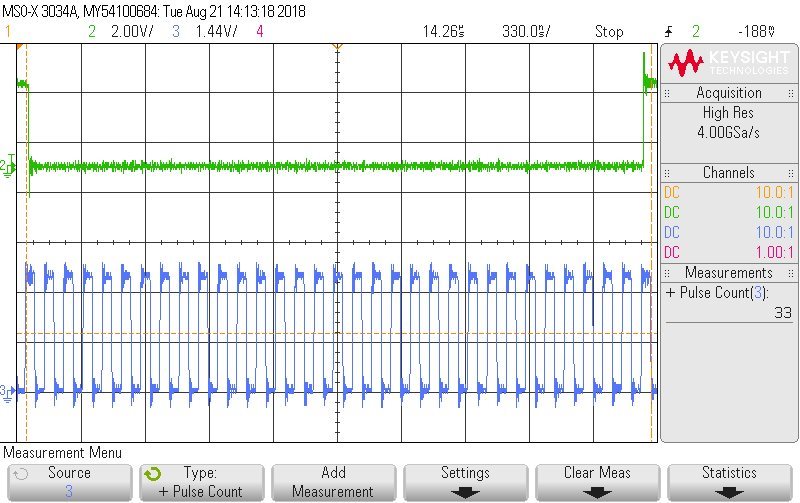

I have used SDFM + AMC1303E2520 on a previews project without problems, but now I have problems with getting correct data. I have an interrupt set (like in examples) and I just read the data and save it. I'm measuring nothing (but I have resistors - shunt and voltage ladder connected) so I would expect to constantly measure 0+/-some noise.

And for voltage I get something like that. But for current I get spikes every now and then. They are both on SDFM1 module, configured the same. As seen in attacked pictures. On the picture is IL1 and UL1. The same exact situation is for other phase currents and voltages.

Any ideas why?