Hi,

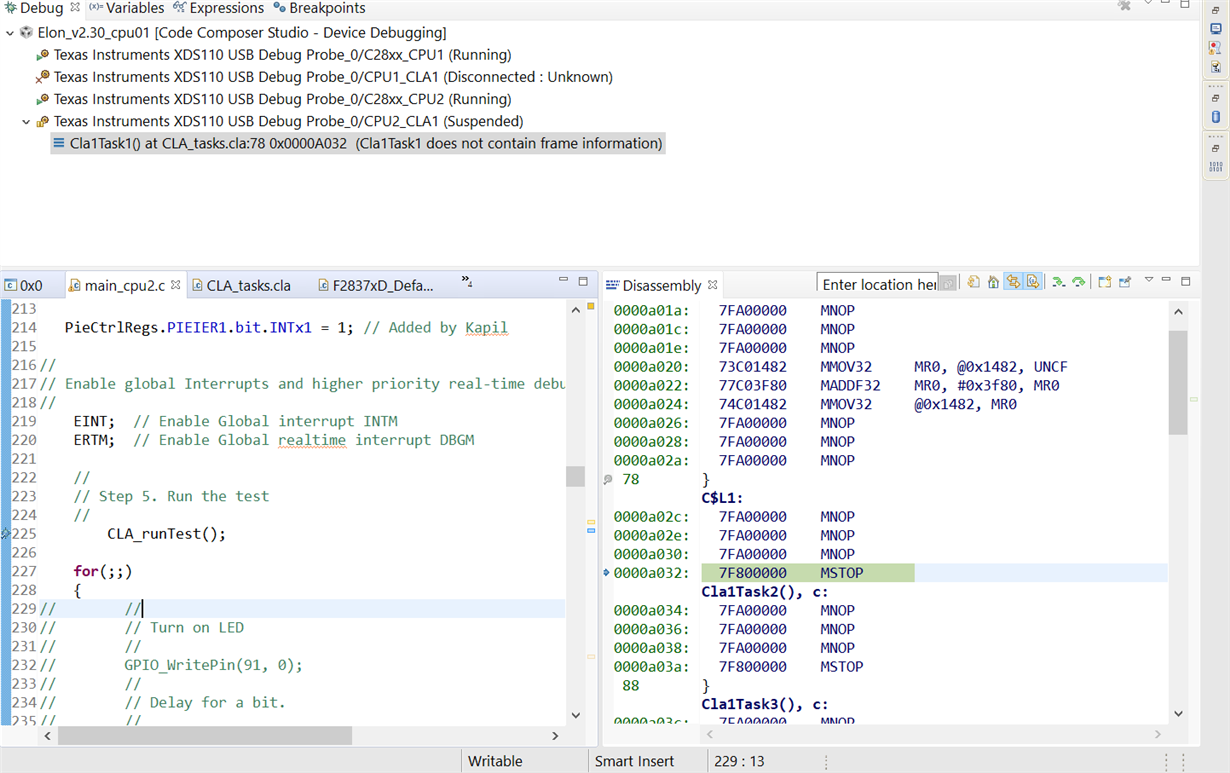

I am trying to use cla of cpu2. I took example code "cla_iir2p2z_dc_cpu01" & "cla_iir2p2z_dc_cpu01" as reference. When I try to debug this code, initially "CLA_runTest();" function is executed and it is entering cla_task1 as it is expected. After its completion CLA is halted and when I select CPU2_CLA1 and run, it is showing error as

CPU2_CLA1: Can't Run Target CPU: (Error -2060 @ 0x0) Requested operation cannot be done while device is running. Halt the device, and retry the operation. (Emulation package 7.0.100.0)

Also, as shown in below attachment, it is showing that Cla1Task1 doesnot contain frame information.

What does this mean? How can I debug CLA?

Regards,

Lowkya