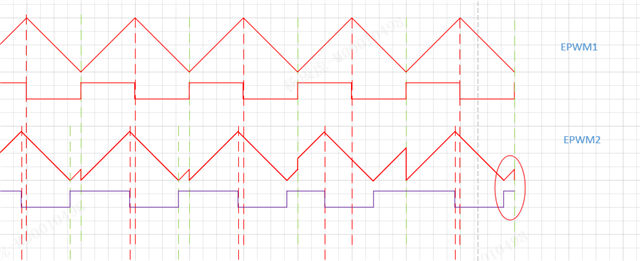

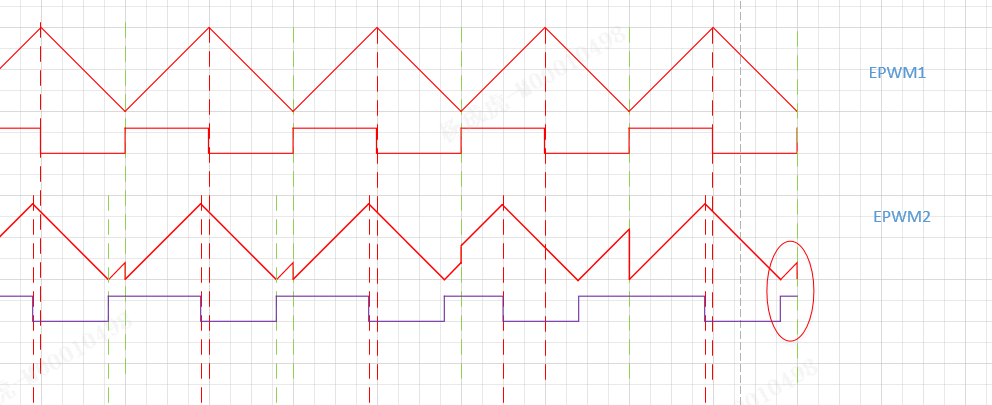

I want to use EPWM1/2/3 to phase shift convter, EPWM1 is master, EPWM2/3 is slave.

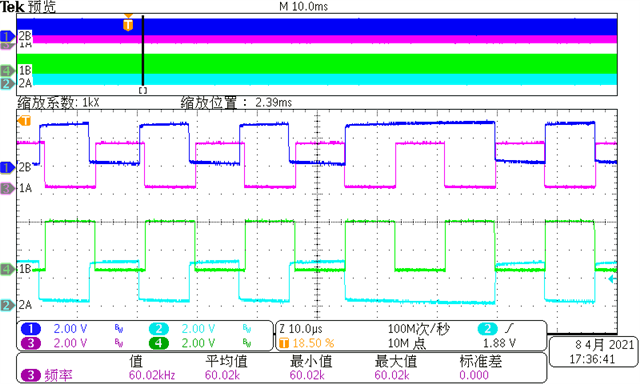

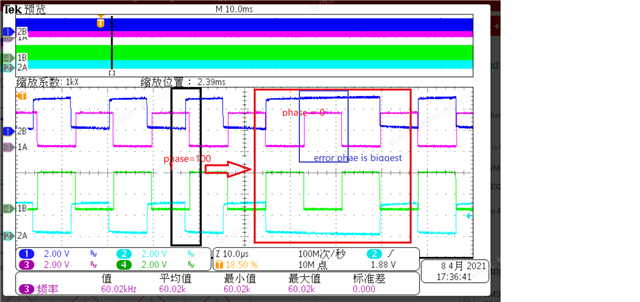

but EPWM2 do not work well,if I enable phase(EPWM_enablePhaseShiftLoad(EPWM2_BASE);), TBCTR is working and beyond TBPRD,it seems not sync to EPWM1;if disable PSEN,TBCTR is normal.

I find the similar question about phase shift , it has a different.

my configuration is here.

EPWM1 configuration:

EALLOW;

EPWM_setPeriodLoadMode(EPWM1_BASE, EPWM_PERIOD_SHADOW_LOAD);

EPWM_setTimeBasePeriod(EPWM1_BASE, DCDC_PSFB_PRD_NOR);

EPWM_setTimeBaseCounter(EPWM1_BASE, 0);

EPWM_setPhaseShift(EPWM1_BASE, 0);

EPWM_setTimeBaseCounterMode(EPWM1_BASE, EPWM_COUNTER_MODE_UP_DOWN);

EPWM_setClockPrescaler(EPWM1_BASE, EPWM_CLOCK_DIVIDER_1, EPWM_HSCLOCK_DIVIDER_1);

EPWM_setCounterCompareValue(EPWM1_BASE, EPWM_COUNTER_COMPARE_A, 0);

EPWM_setCounterCompareValue(EPWM1_BASE, EPWM_COUNTER_COMPARE_B, 0);

EPWM_setCounterCompareShadowLoadMode(EPWM1_BASE, EPWM_COUNTER_COMPARE_A,EPWM_COMP_LOAD_ON_CNTR_ZERO);

EPWM_setCounterCompareShadowLoadMode(EPWM1_BASE, EPWM_COUNTER_COMPARE_B,EPWM_COMP_LOAD_ON_CNTR_ZERO);

EPWM_setActionQualifierAction(EPWM1_BASE, EPWM_AQ_OUTPUT_A ,EPWM_AQ_OUTPUT_HIGH, EPWM_AQ_OUTPUT_ON_TIMEBASE_ZERO);

EPWM_setActionQualifierAction(EPWM1_BASE, EPWM_AQ_OUTPUT_A ,EPWM_AQ_OUTPUT_LOW, EPWM_AQ_OUTPUT_ON_TIMEBASE_PERIOD);

EPWM_setDeadBandCounterClock(EPWM1_BASE, EPWM_DB_COUNTER_CLOCK_FULL_CYCLE);

EPWM_setRisingEdgeDelayCount(EPWM1_BASE, LEAD_RED);

EPWM_setFallingEdgeDelayCount(EPWM1_BASE, LEAD_FED);

EPWM_setDeadBandDelayMode(EPWM1_BASE, EPWM_DB_RED, true);

EPWM_setDeadBandDelayMode(EPWM1_BASE, EPWM_DB_FED, true);

EPWM_setRisingEdgeDeadBandDelayInput(EPWM1_BASE, EPWM_DB_INPUT_EPWMA);

EPWM_setFallingEdgeDeadBandDelayInput(EPWM1_BASE, EPWM_DB_INPUT_EPWMA);

EPWM_setDeadBandDelayPolarity(EPWM1_BASE, EPWM_DB_RED,EPWM_DB_POLARITY_ACTIVE_HIGH);

EPWM_setDeadBandDelayPolarity(EPWM1_BASE, EPWM_DB_FED,EPWM_DB_POLARITY_ACTIVE_LOW);

EPWM_disablePhaseShiftLoad(EPWM1_BASE);

EPWM_setSyncOutPulseMode(EPWM1_BASE, EPWM_SYNC_OUT_PULSE_ON_COUNTER_ZERO);

EPWM2 configuration:

EALLOW;

EPWM_setPeriodLoadMode(EPWM2_BASE, EPWM_PERIOD_SHADOW_LOAD);

EPWM_setTimeBasePeriod(EPWM2_BASE, DCDC_PSFB_PRD_NOR);

EPWM_setTimeBaseCounter(EPWM2_BASE, 2);

EPWM_setPhaseShift(EPWM2_BASE, 2);

EPWM_setTimeBaseCounterMode(EPWM2_BASE, EPWM_COUNTER_MODE_UP_DOWN);

EPWM_setClockPrescaler(EPWM2_BASE, EPWM_CLOCK_DIVIDER_1, EPWM_HSCLOCK_DIVIDER_1);

EPWM_setCounterCompareValue(EPWM2_BASE, EPWM_COUNTER_COMPARE_A, 0);

EPWM_setCounterCompareValue(EPWM2_BASE, EPWM_COUNTER_COMPARE_B, 0);

EPWM_setCounterCompareShadowLoadMode(EPWM2_BASE, EPWM_COUNTER_COMPARE_A,EPWM_COMP_LOAD_ON_CNTR_ZERO);

EPWM_setCounterCompareShadowLoadMode(EPWM2_BASE, EPWM_COUNTER_COMPARE_B,EPWM_COMP_LOAD_ON_CNTR_ZERO);

EPWM_setActionQualifierAction(EPWM2_BASE, EPWM_AQ_OUTPUT_A ,EPWM_AQ_OUTPUT_HIGH, EPWM_AQ_OUTPUT_ON_TIMEBASE_ZERO);

EPWM_setActionQualifierAction(EPWM2_BASE, EPWM_AQ_OUTPUT_A ,EPWM_AQ_OUTPUT_LOW, EPWM_AQ_OUTPUT_ON_TIMEBASE_PERIOD);

EPWM_setDeadBandCounterClock(EPWM2_BASE, EPWM_DB_COUNTER_CLOCK_FULL_CYCLE);

EPWM_setRisingEdgeDelayCount(EPWM2_BASE, LEAD_RED);

EPWM_setFallingEdgeDelayCount(EPWM2_BASE, LEAD_FED);

EPWM_setDeadBandDelayMode(EPWM2_BASE, EPWM_DB_RED, true);

EPWM_setDeadBandDelayMode(EPWM2_BASE, EPWM_DB_FED, true);

EPWM_setRisingEdgeDeadBandDelayInput(EPWM2_BASE, EPWM_DB_INPUT_EPWMA);

EPWM_setFallingEdgeDeadBandDelayInput(EPWM2_BASE, EPWM_DB_INPUT_EPWMA);

EPWM_setDeadBandDelayPolarity(EPWM2_BASE, EPWM_DB_RED,EPWM_DB_POLARITY_ACTIVE_HIGH);

EPWM_setDeadBandDelayPolarity(EPWM2_BASE, EPWM_DB_FED,EPWM_DB_POLARITY_ACTIVE_LOW);

EPWM_enablePhaseShiftLoad(EPWM2_BASE);

EPWM_setSyncOutPulseMode(EPWM2_BASE, EPWM_SYNC_OUT_PULSE_ON_COUNTER_ZERO);

EPWM_setSyncOutPulseMode(EPWM2_BASE, EPWM_SYNC_OUT_PULSE_ON_EPWMxSYNCIN);

EPWM_setPhaseShift(EPWM2_BASE, 250);

EPWM_setCountModeAfterSync(EPWM2_BASE, EPWM_COUNT_MODE_UP_AFTER_SYNC);