Hello everyone! I am new with micro-controller and I have problems when establishing SPI interface between MSPF449 and KXPS5 accelerometer ( Kionix Inc.).

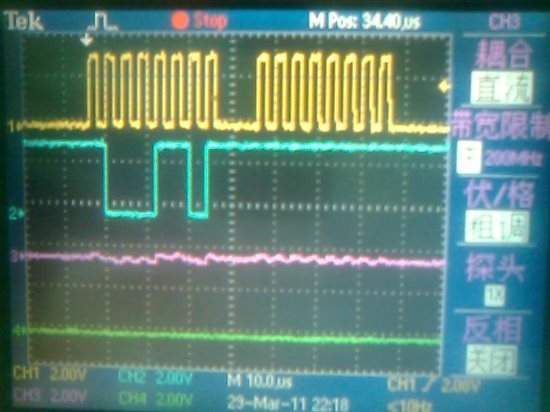

Here is the problem .I want to read back the content of KXPS5’s register. However, I could not get any useful data back. There is always 0x00 data on the MISO line. I think the initializing of the master is correct, because the data on SCK line and MOSI line appear correct (using oscillator). Maybe the initializing of the accelerometer is not correct, but I could not figure out.

The following are the connection and the code. //********************************************************* // MSP430x44x kionix KX_S5 // -------------| // | P4.4 |---> nCS // | UCLK/P3.3 |--->SCLK // | SOMI/P3.2 |<---SDO // | SIMO/P3.1 |--->SDI // | P4.6 |--->Enable // //********************************************************** #include <MSP430x44x.h> unsigned char control[4]={0x8D,0xFF,0x8C,0xFF}; // read command:0x8D and 0x8C are the address of two register in KXPS5 ; // 0xFF is dummy data send to KXPS5 unsigned char receive[4]={0xFF,0xFF,0xFF,0xFF}; // saving the data read back from KXPS5 unsigned char j=0; void SPI_transfer(unsigned char txbyte) { IFG1 |= URXIFG0; IE1 |= URXIE0; } void wait (int counts) { __no_operation(); do (counts--); while (counts != 0); } int main(void) { WDTCTL = WDTPW + WDTHOLD; SCFI0 |= FN_4; //ACLK = LFXT1 =32768Hz //MCLK = SMCLK =DCOCLK = (N+1)*2*ACLK SCFQCTL = 121; //(121+1)*32768*2=7.99MHz FLL_CTL0 = DCOPLUS + OSCCAP1; P3SEL = 0x0E; // Setup P3 for SPI mode P3DIR |= 0x0A; U0CTL = CHAR + SYNC + MM + SWRST; // 8-bit, SPI, Master U0TCTL = CKPL + SSEL1 + STC; // Polarity, 3-wire , // all the 4 clock mode I have tried, but nothing changed on the SOMI line. U0BR0 = 0x010; // SPICLK = SMCLK/2 = 4MHz U0BR1 = 0x000; U0MCTL = 0x000; ME1 = USPIE0; // Module enable U0CTL &= ~SWRST; // SPI enable P4DIR |= BIT6 + BIT4; P4OUT |= BIT4; P4OUT &= ~BIT6; // slave ENABLE P4OUT |= BIT6; wait (5000); _EINT(); // Enable interrupts while(1) { P4OUT |= BIT4; for (j=0;j<4;j++) { P4OUT |= BIT4; SPI_transfer (control[j]); } LPM0; // CPU off } } #pragma vector=USART0RX_VECTOR __interrupt void SPI0_rx (void) { P4OUT &= ~BIT4; // chip select //slave SPI enable TXBUF0 = control[j]; while ((IFG1 & URXIFG0) == 1); // RX/TX ready? receive[j]=RXBUF0; j = j + 1; TXBUF0 = control[j]; while ((IFG1 & URXIFG0) == 1); // RX/TX ready? wait (200); receive[j]=RXBUF0; P4OUT |= BIT4; IE1 &= ~URXIE0; } Here is the datasheet for KXPS5. http://www.kionix.com/Product-Specs/KXSS5-2057%20Specifications%20Rev%203.pdf Please help me on this. Thank you very much!

PS: I am using both evaluation board of MSP430F449 and KXPS5.