Tool/software: Code Composer Studio

Dear colleagues,

I was wondering if someone has more details about the sample and hold (S&H) circuit of the embedded ADC.

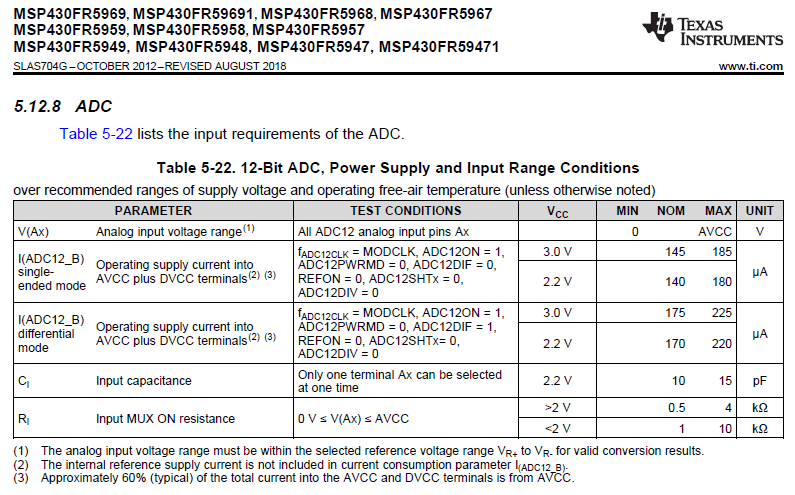

I suppose that the S&H has a switch to do the sampling and a capacitor to hold the voltage. How much are the on-resistance of this switch and the holding capacitance? In the datasheet, the only values specified are the MUX-on resistance and the input capacitance. Maybe the same “switch” of the MUX is employed to do the sampling, and the input capacitance behaves as a holding capacitance. Is that possible?

Best regards!

Ferran