Other Parts Discussed in Thread: MSP430G2553

Hi, so I designed a simple circuit board that fits on top of the Launchpad. This circuit board has the MCP2515 Can Controller, SN65HVD TI Can Transceiver, and some other basic circuit components.

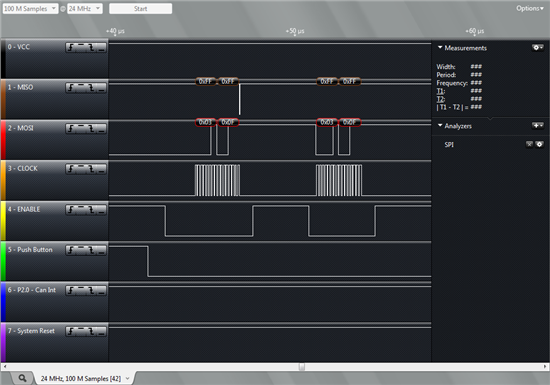

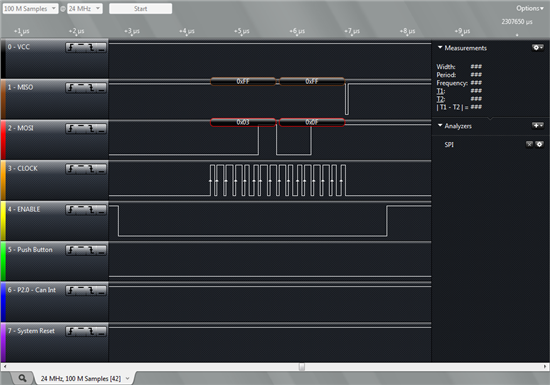

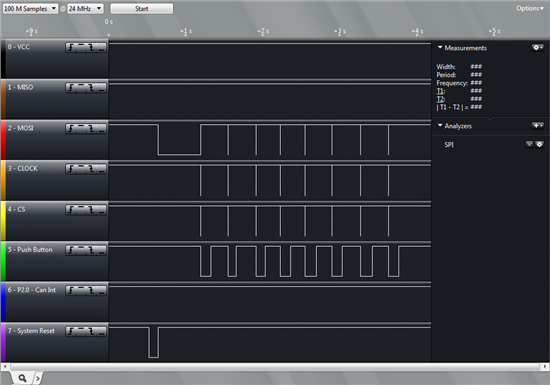

All I am focusing on right now is the SPI. The issue that I am having is that the MISO (master in slave out) line is always logic high. The other lines, SCK, MOSI, STE, all work fine.

I wrote a simple program for the Launchpad that, upon pushing the P1.3 button, sends a "Read Register" instruction to the MCP2515. This instruction is then sent a second time, and that is the end of the program.

All communication lines are fine, except for MISO, which is stuck at logic high. After lots of playing around, I ran into a situation where the MISO line went low for a very short instant (~40 ns), and then back to high.

Attached to this post are a picture of the schematic of my circuit board (R4 not connected), two pictures showing the waveform that I got from the Logic Analyzer, and printed below is the code that I used.

I appreciate any help that I can get and I am happy to provide any additional information or clarifications that may be needed.

Thank You.