I have an application using the MSP430F5324 as a SPI slave device on UCA0. I've suspected for a while that there is an issue with the device when trying to use it with my SPI configuration that I've selected, and finally had the time to confirm it via dev kit. I used a MSP-TS430RGC64B dev board with a MSP430F5324 in the socket and a Totalphase Aardvark I2C/SPI host adapter. I connected SCLK to P2.7, SIMO to P3.3 and SOMI to P3.4.

The master's SPI configuration is MSB-first bit-order, CLK=125kHz, Polarity="Rising/Falling", Phase="Sample/Setup". According to the Aardvark documentation, this means the following:

- The polarity option specifies which transition constitutes the leading edge and which transition is the falling edge. For example, "rising/falling" would configure the SPI to idle the SCLK clock line low. The clock would then transition low-to-high on the leading edge and high-to-low on the trailing edge.

- The phase option determines whether to sample or setup on the leading edge. For example, "sample/setup" would configure the SPI to sample on the leading edge and setup on the trailing edge.

Here is the code for the simple test program on the MSP430 side, in its entirety:

#include <msp430.h>

int main(void)

{

// Stop watchdog timer to prevent time out reset

WDTCTL = WDTPW + WDTHOLD;

UCA0CTL1 |= UCSWRST;

UCA0CTL0 = UCCKPH|UCMSB|UCMODE_0|UCSYNC;

UCA0STAT = 0u;

UCA0IE = 0u;

UCA0CTL1 &= ~UCSWRST;

P2SEL |= BIT7;

P3SEL |= BIT4|BIT3;

P2DIR |= BIT4;

UCA0TXBUF = 0xaau;

for(;;);

return 0;

}

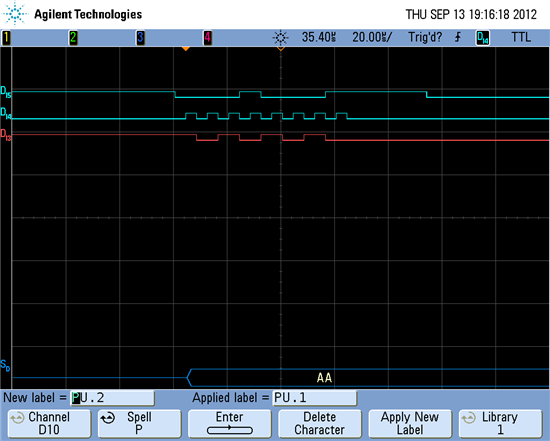

I am performing a simple test of simply transmitting a single byte from the Aardvark GUI tool and watching the SPI bus activity on a scope. What I expect to see is that the MSP430 transmits back 0xaa every time, but what I actually see is the following sequence of transmissions:

0xaa, 0x55, 0x2a, 0x95, 0x4a, 0xa5, 0x52, 0xa9, 0x54, 0xaa

It appears the TXBUF contents are being transmitted shifted to the right by one position each time, with sometimes an MSb being OR-d in. I would say that its a pure rotation of the TXBUF register but there appears to be a 9th bit through which the rotation must be occurring in order to produce the sequence seen.

Below are a couple of scope captures showing simple successive byte transmissions.

Does anyone have any idea what the issue here is? I couldnt' find anything in the errata regarding this behavior.