Dear Sir,

I have Some doubts on MSP430G2 Launch pad Spy-Bi wire and MSP-FET430UIF Spy-Bi wire, Both of these interface’s are doing same work

1. what are the difference between MSP430G2 Launch Pad Spy-Bi wire Interfacing and JTAG or MSP-FET430UIF

Interfacing.

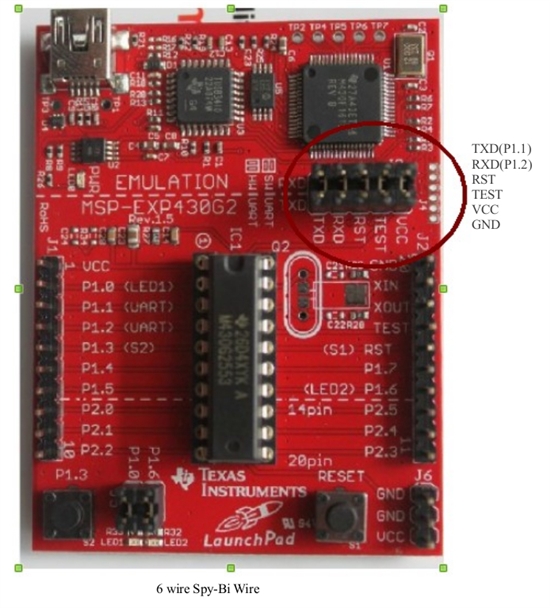

2. and here I have Inserted two of the MSp430 Interfacing Images.

I know this much about These two interfacer.

In JTAG Interfacing following pins connecting to MSP430 External IC

JTAG Pins MSP430 pins TDO - P1.7 TDI - P1.6 TMS - P1.5 TCK - P1.4

RESET

TEST

VCC

GND

In MSP430G2 Launch Pad Spy-Bi wire following pins connecting to MSP430 External IC

Spy-Bi MSP430 pins

RXD P1.1

TXD P1.2

RESET

TEST

VCC

GND

If any mistakes Please sorry.

Thank you.