Other Parts Discussed in Thread: MSP430F5529, MSP430F5438A

I would like to get a confirmation that:

Statement:

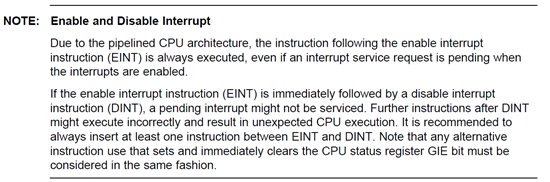

If a DINT is placed after an EINT, at least one instruction must be inserted in-between.

example:

EINT

NOP

DINT

NOP

Reason is that EINT executes the next instruction before servicing any interrupts, but the actual behavior on our f5437(non-A) gives some unpredictable behavior if there is no instructions like NOP in-between EINT and DINT - and an interrupt is pending.

Can anyone confirm our experience ?