Other Parts Discussed in Thread: MSP430WARE

Hello,

I have encountered I2C communication problem that I haven't been able to solve for a while.

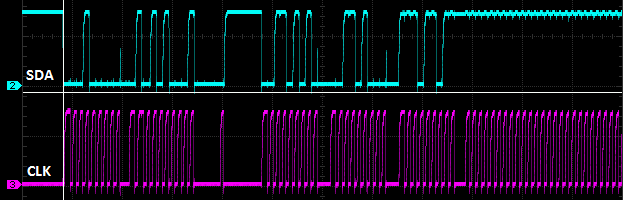

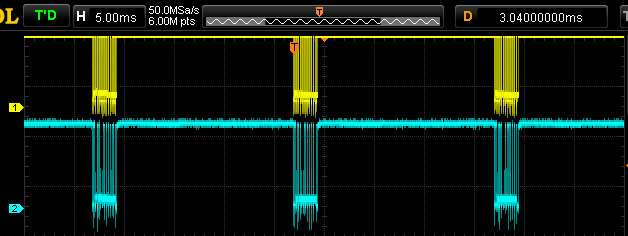

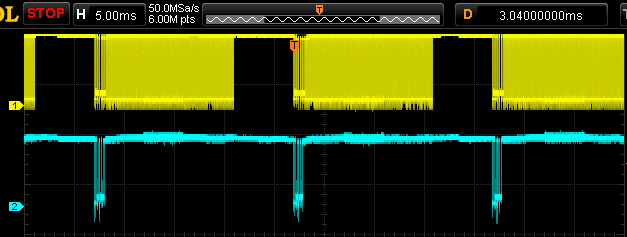

I am using MSP430g2553 to communicate with Bosch BNO055 sensor using their provided C library. In normal conditions I can set up the sensor and read the required data - communication is working fine. However, if the supply voltage of sensor node (for both MSP and BNO055) drops, then starting around 3V at a random time BNO055 often fails to respond and the I2C communication hangs. Weird part is that the MSP430G2553 keeps generating CLK signal seemingly forever (see attached wave forms) while the code has hanged on something like while(!(IFG2 & UCB0RXIFG)) in my I2C subroutine.

I can't figure out:

-why MSP keeps generating CLK when it has hanged on a single code line?

-why the BNO055 stops responding in the first palce?

I implemented kind of a guard timer that resets the communication after some timeout interval so the code at least doesn't hang completely, however, if the supply voltage is <3V (but still within specs of both MSP and BNO055) then most of the time I can read only couple of bytes till this happens.

In my application I am interested in running the sensor node on as low supply voltage as possible as I need to power it along relatively long power supply lines that introduce voltage drop. However, even around 3V I start to get problems and if dropping lower communication fails most of the time making continuous data stream impossible.

Any help in understanding the behavior of MSP and/or BNO055 would be greatly appreciated.

Thank you in advance,

Atis

P.S. I have checked with oscilloscope power supply line and it doesn't seem to have any sudden drops when the problem occurs. I'm also aware of the BNO055 clock stretching - its annoying, but doesn't seem to cause the problem.