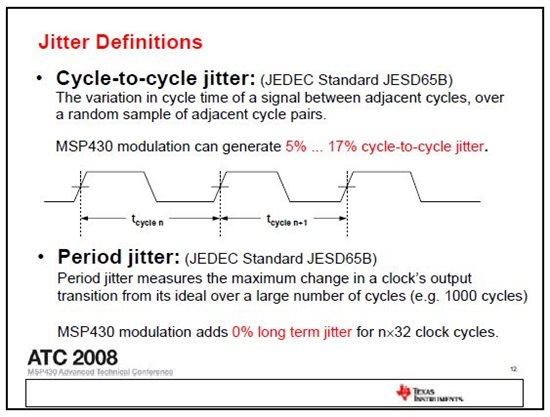

Here is the problem. We need to use a timer to sync to an input signal frequency. We have the timer running at 2Mhz and with 16 bits, we should be able to get down to .5 us resolution. So we will expect to see a small drift. But this is not what I am seeing. The clock appears to have about 25us of high freq jitter and about 10-15us low freq jitter. So the problem is that we can not pick a value that will keep us in the .5us range. To prove this, we connected an external 8 Mhz xtal. With this xtal, I can find a value that keeps the drift down to 325us per minute, that's a 5us drift per second. This is what we need. So, first can we get a specification on the internal oscillator jitter? Also, is there an app note on improving the quality of the oscillator?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.