hi,

I am using register level example code from TI: MSP430FR243x Demo - eUSCI_B0 I2C Master TX bytes to Multiple Slaves.

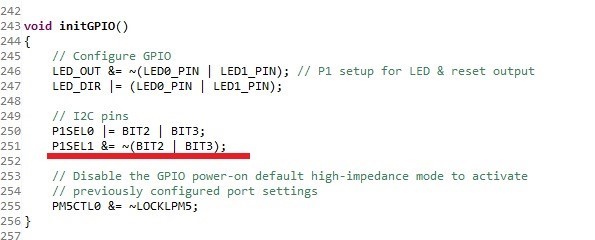

What i noticed is when it executed to line 250: 1SEL0 |=BIT2 | BIT3, both SCL and SDA did pull high to 3.3V.

However, once it executed to line 251: P1SEL1 &=~(BIT2 | BIT3), I noticed the SCL line will go low. What is the reason SCL line P1.3 go low after line 251? This is just the initialisation of the i2C GPIO ports. No reason why it should go low. I am expecting both SCL and SDA I2C lines to be high.

Please advice.

Best regards,

KPK

My full test code attached.