Hello team,

I'm working with WDT and facing problem in configuring WDT for near to 15msec.

I want my clock to be 24Mhz WDT reset timings is ~15msec for WDT can use any clock source. Please someone suggest in configuring WDT.

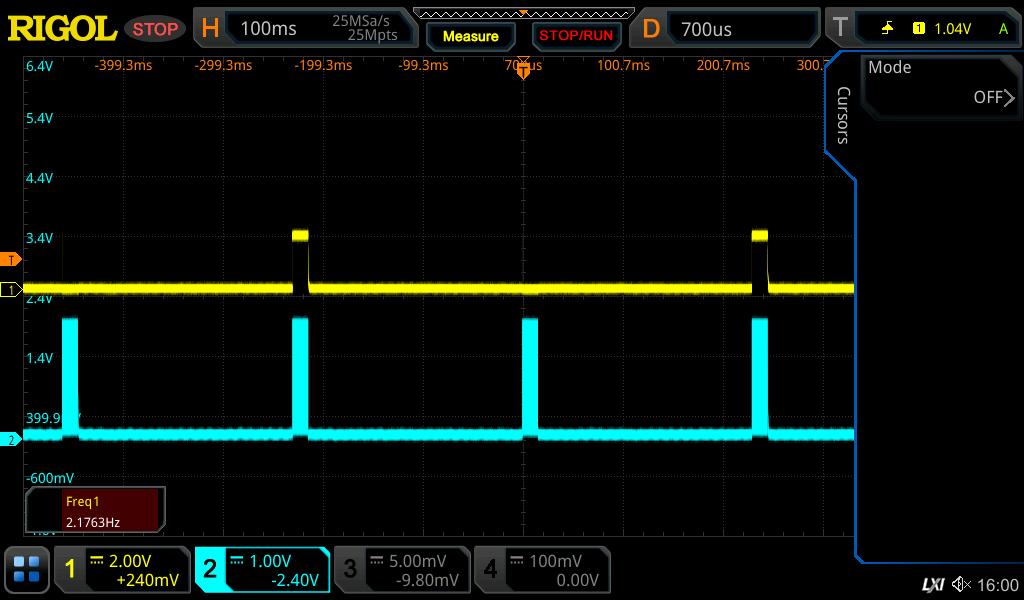

I already tried with below code and failed. The behaviour of WDT is unpredictable. Someone explain me why?

#include <msp430.h>

void clock_setup(void);

int main(void)

{

WDTCTL = WDTPW | WDTHOLD; // Stop WDT

clock_setup();

P1DIR |= BIT0;// Set P1.0 to output direction

P6DIR |= BIT6;

P1OUT ^= BIT0;

PM5CTL0 &= ~LOCKLPM5; // Disable the GPIO power-on default high-impedance mode

// to activate previously configured port settings

WDTCTL = WDTPW | WDTSSEL_1 | WDTCNTCL | WDTTMSEL_0 | WDTIS_6; // WDT 32ms, SMCLK, interval timer

// __no_operation(); // For debug

while (1)

{

P6OUT ^= BIT6; // Toggle LED

}

}

void clock_setup()

{

// Setting clock to 24Mhz

P2SEL1 |= BIT6 | BIT7; // P2.6~P2.7: crystal pins

FRCTL0 = FRCTLPW | NWAITS_2; // FRAM: 2 wait states

do

{

CSCTL7 &= ~(XT1OFFG | DCOFFG); // Clear XT1 and DCO fault flag

SFRIFG1 &= ~OFIFG;

}

while (SFRIFG1 & OFIFG); // Test oscillator fault flag

__bis_SR_register(SCG0); // disable FLL

CSCTL3 |= SELREF__XT1CLK; // Set XT1 as FLL reference source

CSCTL0 = 0; // clear DCO and MOD registers

CSCTL1 = DCORSEL_7; // Set DCO = 24MHz

CSCTL2 = FLLD_0 + 731; // DCOCLKDIV = 24MHz

__delay_cycles(3);

__bic_SR_register(SCG0); // enable FLL

while (CSCTL7 & (FLLUNLOCK0 | FLLUNLOCK1))

; // wait till FLL locked

CSCTL4 = SELMS__DCOCLKDIV | SELA__XT1CLK; // set XT1 (~32768Hz) as ACLK source

// default DCOCLKDIV as MCLK and SMCLK source

}