Tool/software: Code Composer Studio

SO this is a two part question:

Firstly, on the MSP430FR6989 board, where are the P3.4 and P3.5 located? I have looked over the board and could not see the markings anywhere.

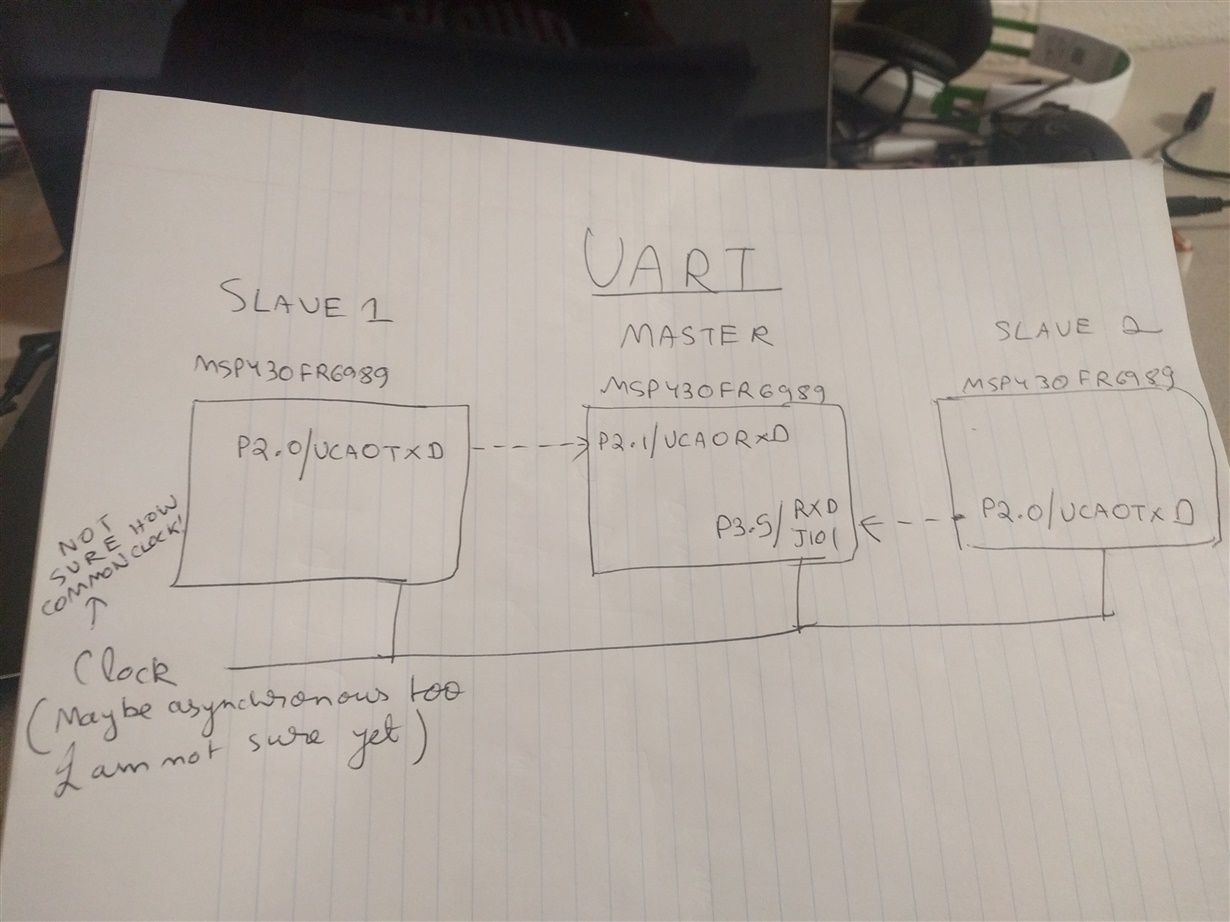

Secondly, is there a good example somewhere on how to set up UART communication in assembler (CCS) between two MSP430s (or one master MSP430 with two slave MSP430s). The example(s) I found in TI Resource Explorer is/are apparently transmitting data to itself and most of the examples online are from MCU to PC.

Thanks in advance.