Other Parts Discussed in Thread: ADS1298, ISO7840, ISO7841, TM4C1294NCPDT

Hi!

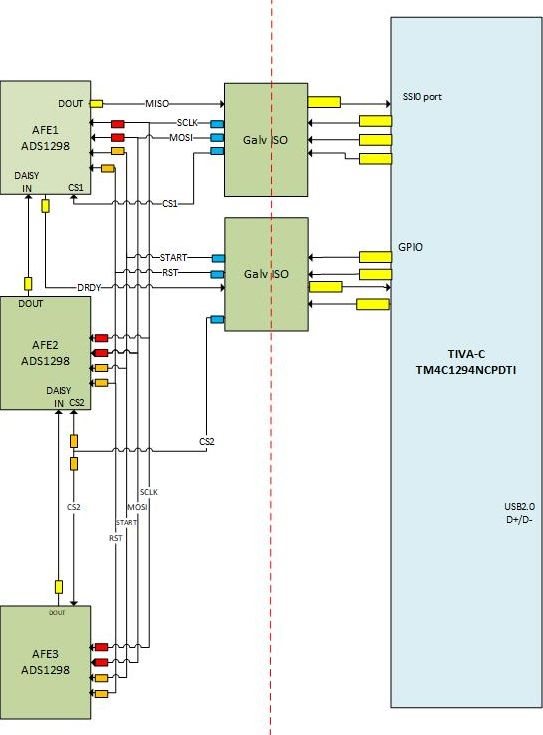

we have a system in which multiple ADS1298 (3pcs) are connected onto the TM4C1294.

The 3pcs ADS1298 are daisy chained together.(with a possibility to Chip select the AFE1, or the AFE2+AFE3 during the initialization/work)

I need a little help regarding the proper termination of the SPI lines(serial termination), especially the SCLK and the MOSI lines (to prevent ringing and to minimize the EMI radiation)

Here is a simplified block diagram.

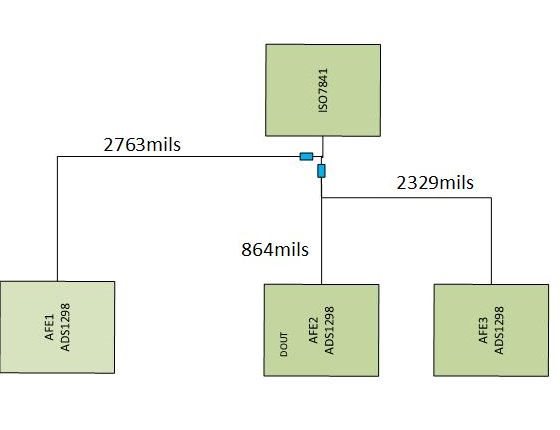

At this point I am sure that the YELLOW termination points are on good place. But i dont know how is the best to terminate the SCLK and the MOSI line as after the galvanic isolation the lines are routed onto 3 ways, and the 3 section does not have the same lengths. The AFE2 and the AFE3 are close together.

So my question is where to put the termination resistors ?

Did i need to put only the at the RED termination points regarding the SCLK, and MOSI, or i need termination also/only at the BLUE points? So to put after the Y split on every leg, or/and before the splitting(too) ?

Same questions i have regarding the other common lines START, RESET, CS, but as these lines wont change their status after the initialization, these lines might not make problems if i put termination only on the BLUE points.

Thanks!

Best Regardss

Lou