Dear Champs,

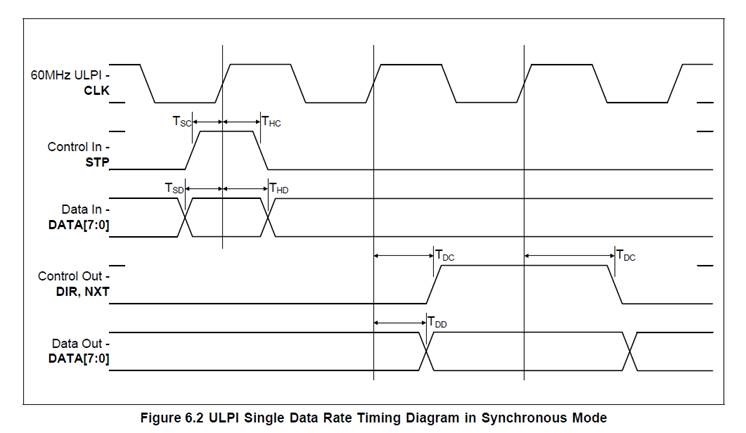

As we check ULPI Interface Timing Diagram in datasheet, we saw below figure:

But it seems have some different with ULPI spec.

And it's also different with Microchip high speed PHY, USB3220C.

Why our ULPI signal need delay U5 when clock rising up? Rather than start up TSC time before clock rising up?

If you have any suggestion, please feel free to let me know.

Thanks a lot.

Best regards,

Janet