Other Parts Discussed in Thread: TM4C1294NCPDT

A couple of very basic questions about non-volatile memories lifetime / endurance:

- Does READING eeprom have any impact on its lifetime? Or is it safe to read it a gazillion times, with the 500,000 limit just for WRITE operations?

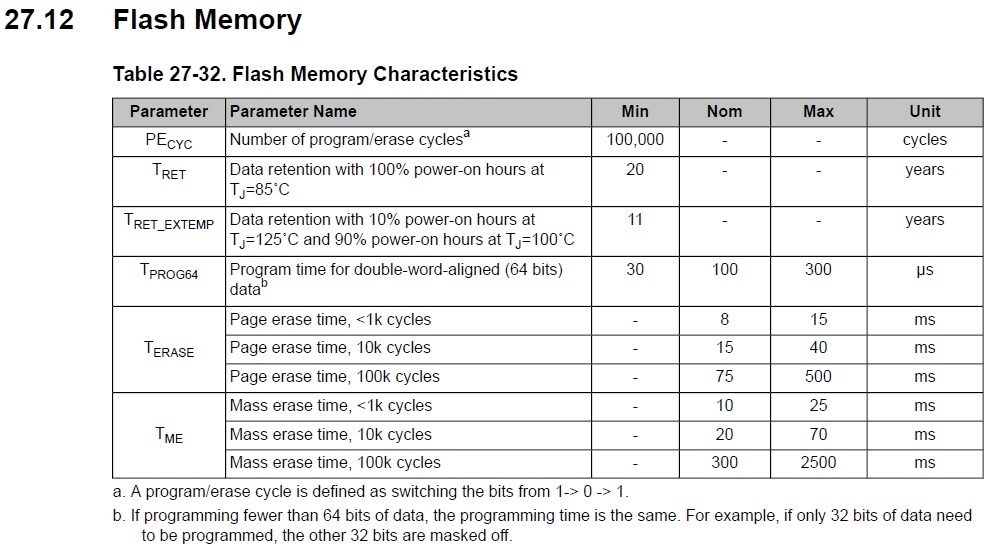

- For WRITE CYCLES, does the FLASH memory have any sort of similar life limitation on TM4C devices such as EEPROM has?

Context: currently working to improve some features of our products, and trying to organize where/how to store a few "status and configuration" parameters that can change from time to time... Let's say one can be concerned that the product will fail after 1370 years if these parameters are rewritten to eeprom once a day...