Hi all,

There is another question in the forum with a similar title, but the solution for that problem is not my case, so here we go again.

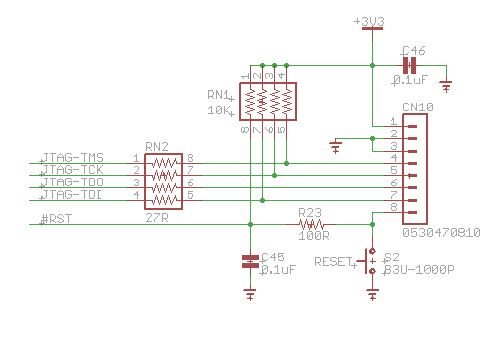

Using IAR, fully updated. The board is a custom project, in which the JTAG is the same as we have been using for other ARM TM4C projects successfully. The JTAG diagram is attached. Do not mind the different picoblade 8-pin connector, as I am triple sure that all pins are where they should go.

The same IAR workbench and project compiles and uploads properly with another board that we have. The problem is hidden somewhere in this new board. We assembled two boards, and both have the exact same result. I supected a bad IC, and replaced the TM4C123AH6PMI chip from one of them, same problem.

The schematics below is the IC part of the board. I checked each 3V3 pin, they are all good (3.24V), each ground pin, they are properly grounded, and the VDDC pins are also coherent (1.095V)

First question: is this the typical signal expected on TDO when the JTAG pin is NOT connected? It is high at 3.24V, with spikes coming down to about 1.7V at 135Hz. With JTAG connected, the shape is similar, but it goes down to approximately 2.5V. Image below:

I have a couple more brand new sample IC's here, from a different shipment, but I am avoiding to replace an IC again, because the first time I did it the result was exactly the same, so maybe someone out there can give me another hint - resoldering IC's are painful for the board...

What else has been checked:

- The pull up resistors are confirmed to be 10K. Measured twice, and replaced twice. No shorts between any of them.

- The 27R resistors are confirmed to be 27R. I even removed them and connected the pads directly to have no resistance. The resistance was confirmed all the way from the IC pins to the JTAG 14-pin header.

- Tried to change the connection option on IAR's J-Link settings from JTAG to SWD, no results.

Thanks in advance for the help!