Other Parts Discussed in Thread: TM4C123GH6PGE

Hi,

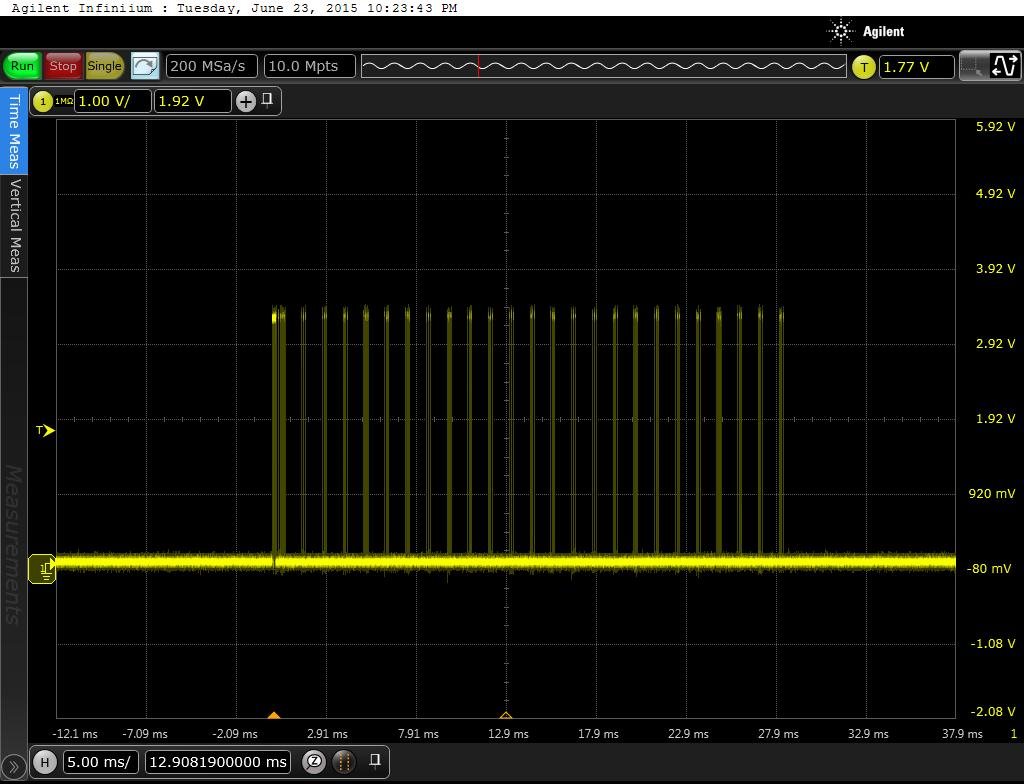

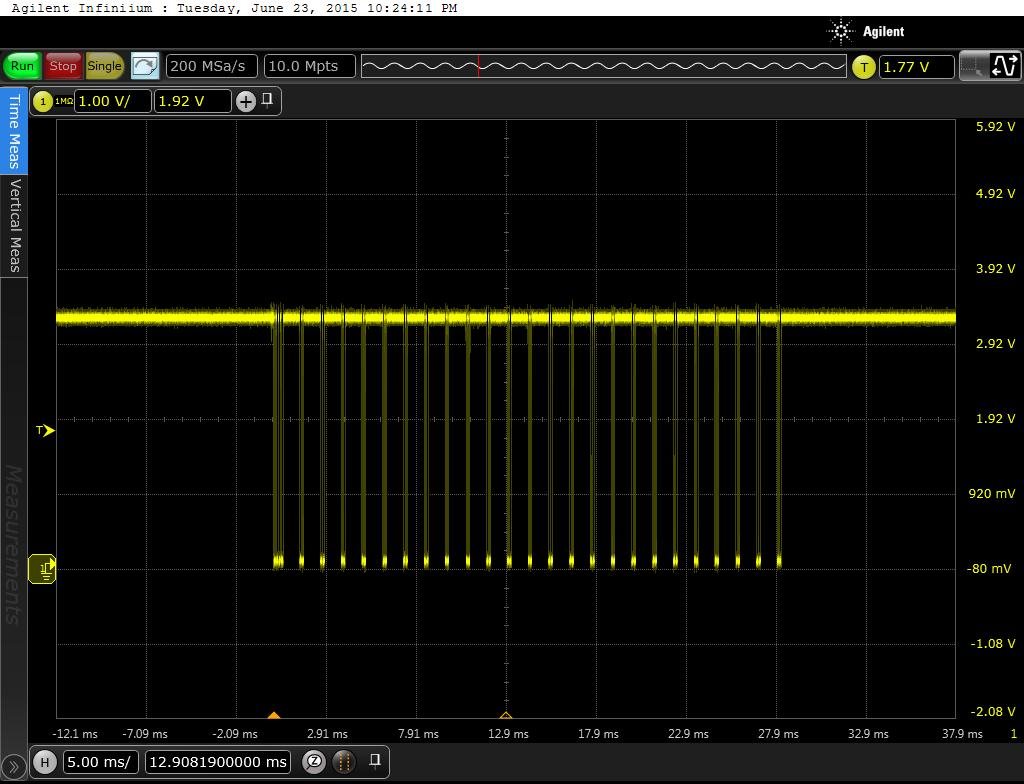

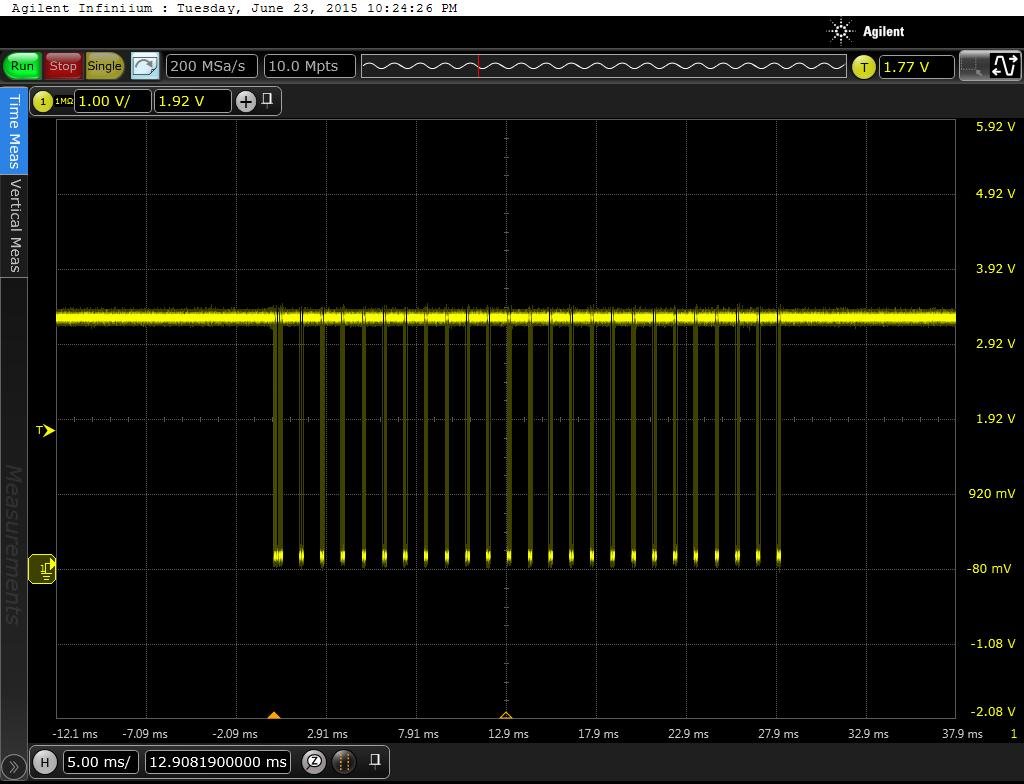

I am using the tm4c123gh6pge MCU, I am trying to flash it with the Tiva C development. When I connect the kit to the board, the JTAG pins TWS, TDI and TDO voltage drop to 2.5 V. However is the PINS aren't connected to the dev kit, the voltage are correct at 3.3 V because of the pull-up