First like to point out a similar issue was previously posted in this link.

https://e2e.ti.com/support/microcontrollers/tiva_arm/f/908/t/359429

Datasheet: 8.2.4.1 BLOCKS

The current block is selected by the EEPROM Current Block (EEBLOCK) register. The current offset is selected and checked for validity by the EEPROM Current Offset (EEOFFSET) register. The application may write the EEOFFSET register any time, and it is also automatically incremented when the EEPROM Read-Write with Increment (EERDWRINC) register is accessed. However the EERDWRINC register does not increment the block number, but instead wraps within the block.

Is it plausible the local bus is accessing the EERDWRINC register when the EEPROM is idle or some kind of refresh is occuring?

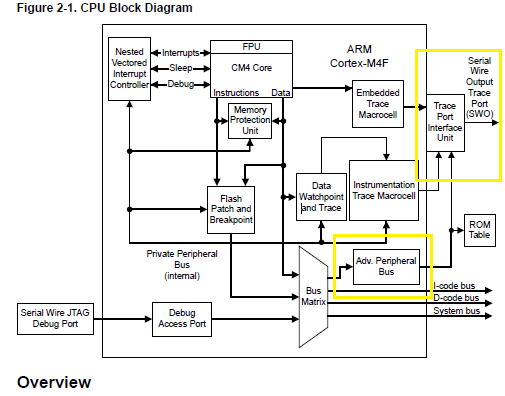

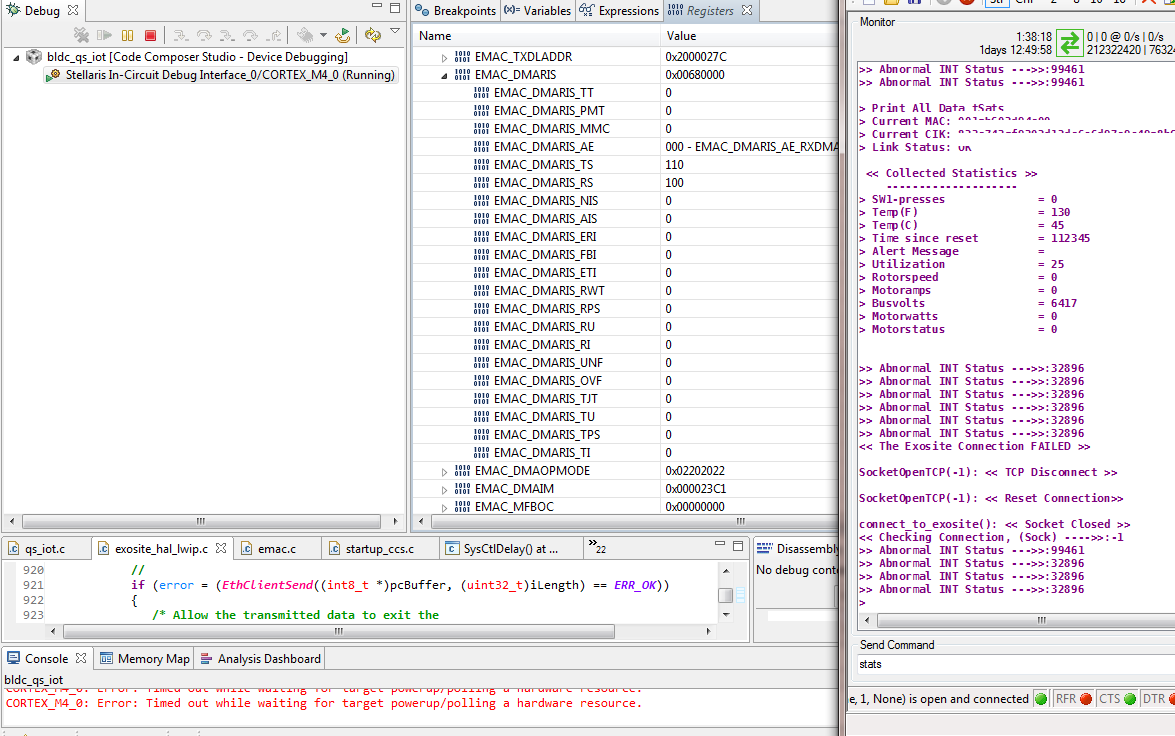

We have a Boolean switch block any EEPROM reads after an SRAM array has been filled with data as to block future reads from EEPROM. CCS debug when EEPROM is actually being read EEOFFSET register has random addressing values and not in a cyclic ring form (-->0,2,4,6,8,A,C,E-->). That same cyclic EEOFFSET ring occurs when ever the application is Paused or during an MPU fault condition. The EERDWR appears in a constant refresh cycling mode following EEOFFSET.