Dear Experts

My customer used TM4C123G on their mother board as I2C master.

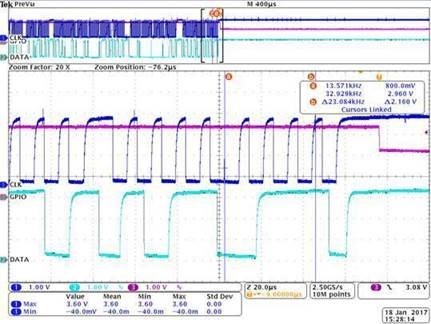

They found when the MCU turn on “I2C glitch filter” function, the communication would be stable.

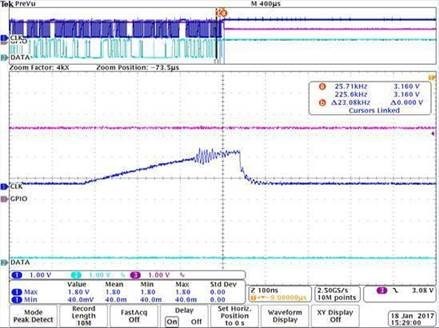

If not, there would be communication problem.

Is there any document talking about why I2C Master would be affected by glitch?

And what the behavior would happen?

On their application, clock would lose when glitch noise is in.

Thanks for your comment.