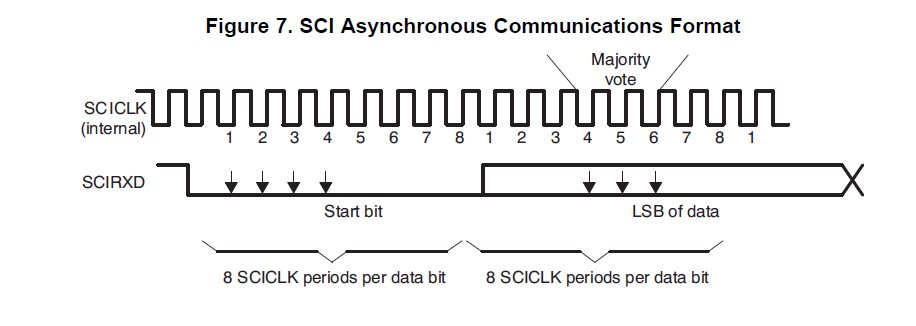

Do we have document to show how UART module to determine the each bit value? I know there are internal 16 or 8 clk samples for each bit, but how many samples could decide the bit value is 0 or 1?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.