Other Parts Discussed in Thread: TM4C1294NCPDT, INA240

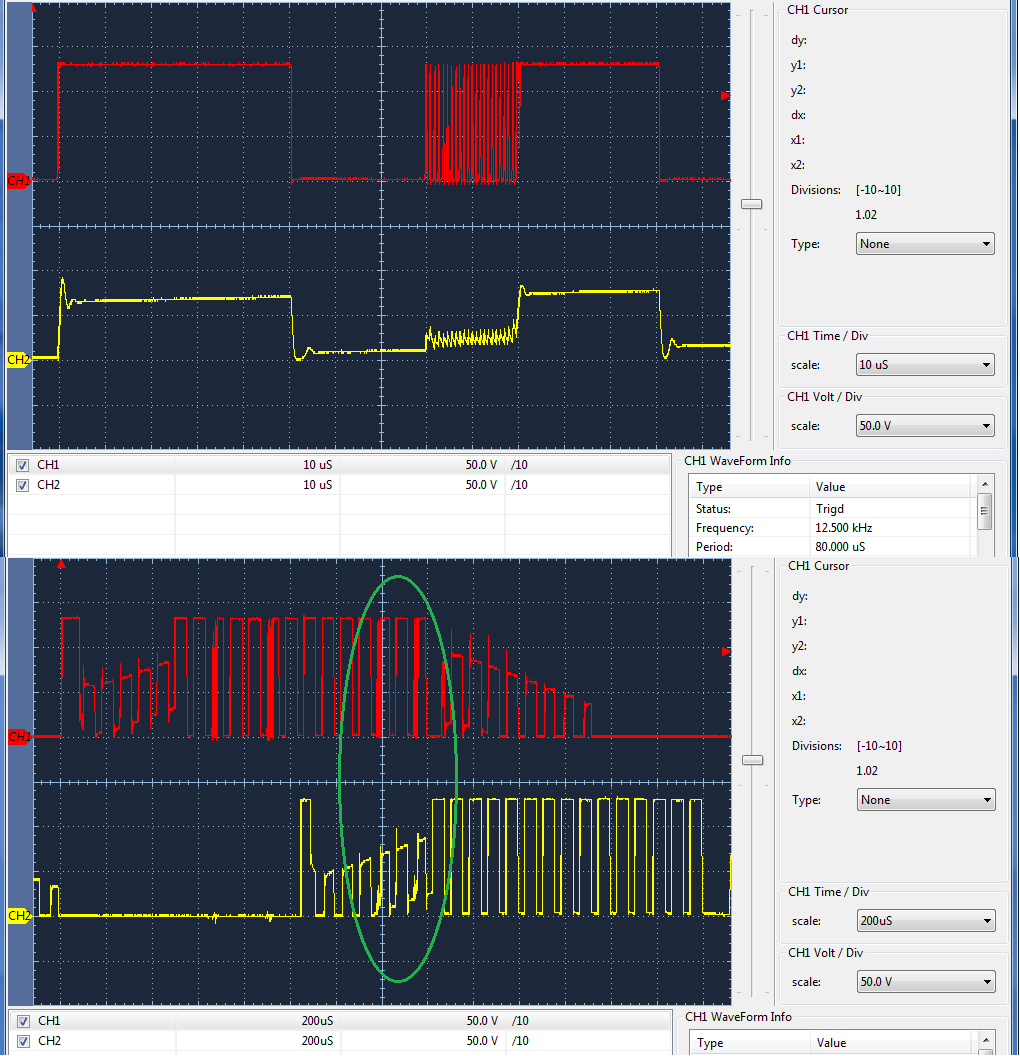

3 PWM generators 1,2,3 but only 2 modulates 80us period having active duty 50us on time (high pulse) where 240ns chopping pulses exist in first 32us of 50us on time. The other generators 1,3 never produce similar chopping pulses but do change rising/falling edge of active on times in the resulting 3 phase inverter wave form. Chopping pulses from generator 2 are seen distinctly via 3phase 1/2 bridge gate drivers reacting to the PWM generators. Otherwise 240ns chopping pulses are hard to imagine in the individual generator edge times.

Perhaps because it requires 2 PWM generators working in concert to produce a proper gate drive pattern for generating a DSP trapezoidal wave shape without 1/2 bridge shoot through occurring.

All three PWM generators are globally synchronous updated via an interrupt from generator 1 upon reaching count zero. Below is the command instructing 3 generators to perform a global synchronous update after a new count is loaded to each generator inside the interrupt handler of generator 1.

Is it wrong for me to think all 3 generators loaded with a similar count prior to an global synchronous update should be producing nearly the same 240ns chopping pulses?

ROM_PWMSyncUpdate(PWM0_BASE, (PWM_GEN_1_BIT|PWM_GEN_2_BIT|PWM_GEN_3_BIT));